# eFPGA-based ML Implementation on Future Collider Detector Readout

**US Higgs Factory Planning**

Kenny Jia, Julia Gonski SLAC National Accelerator Laboratory

Dec 19, 2024

#### OLD PEOPLE VISIONARY SCIENCE REAL IMPACT BOLD PEOPLE VISIONARY SCIENCE REAL IMPACT

### Outline

- 1. Motivation and Physics Context

- 2. eFPGA Technology

- 3. Machine Learning at the Front-End:

- 1. Proof of concept BDT

- 2. Autoencoder for lossy compression and anomaly detection

- 4. Conclusion and Next Steps

BOLD PEOPLE VISIONARY SCIENCE REAL IMPACT BOLD PEOPLE VISIONARY SCIENCE REAL IMPACT

1

### Motivation and Physics Context

### **Motivation and Physics Context**

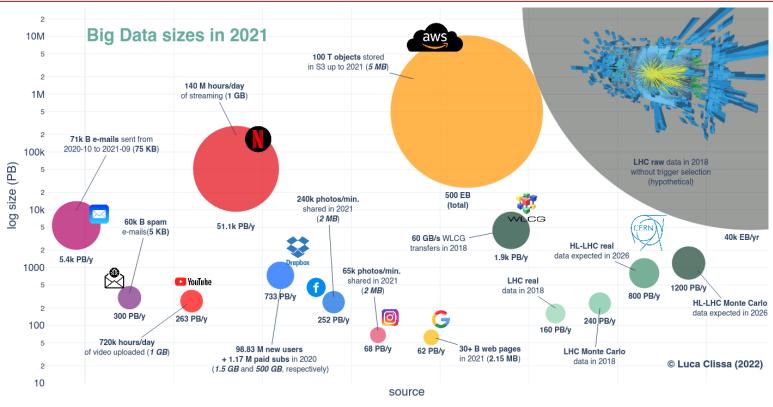

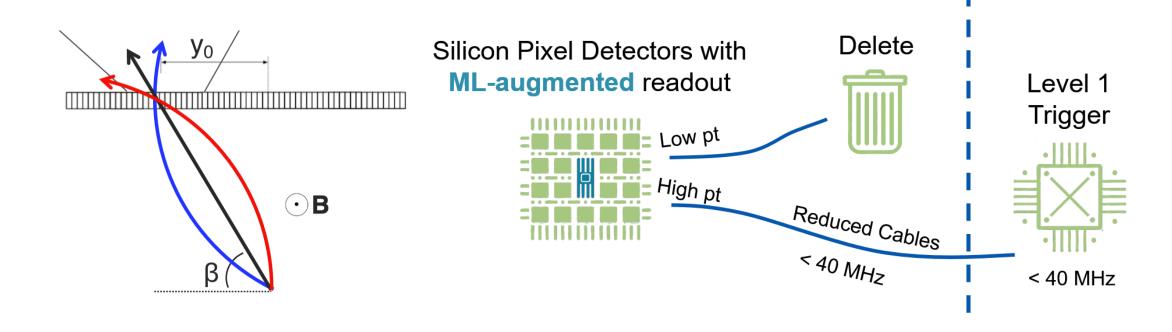

Pixel Detectors on collider:

- O(100) million pixels

- Petabyte per second data rate (more for future colliders!)

Can't send everything off-detector

Challenge: how to effectively reduce the data volume transmitted off-detector while preserving useful physics information as much as possible?

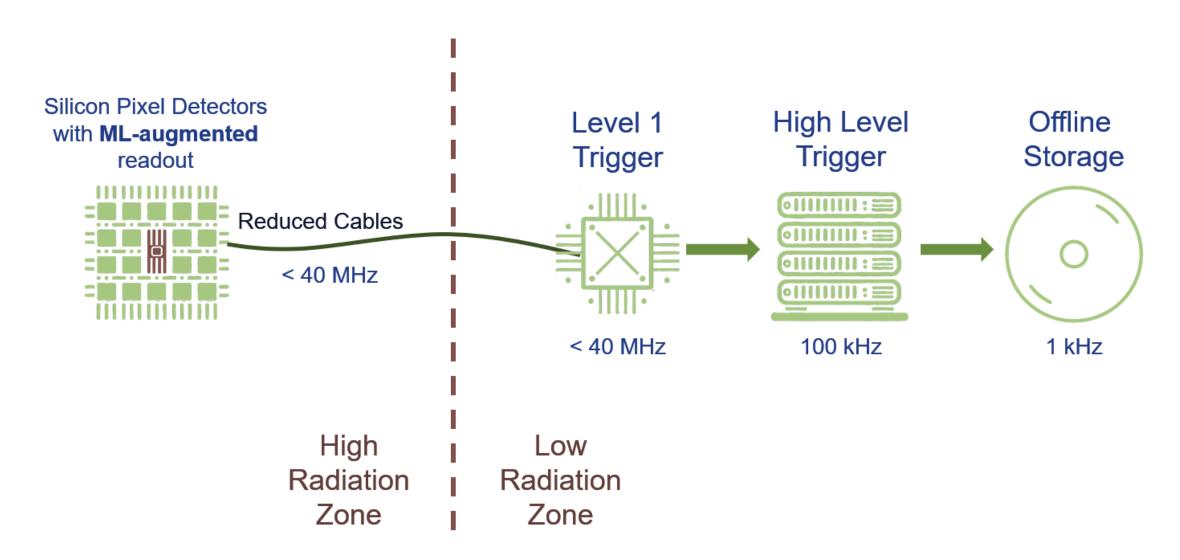

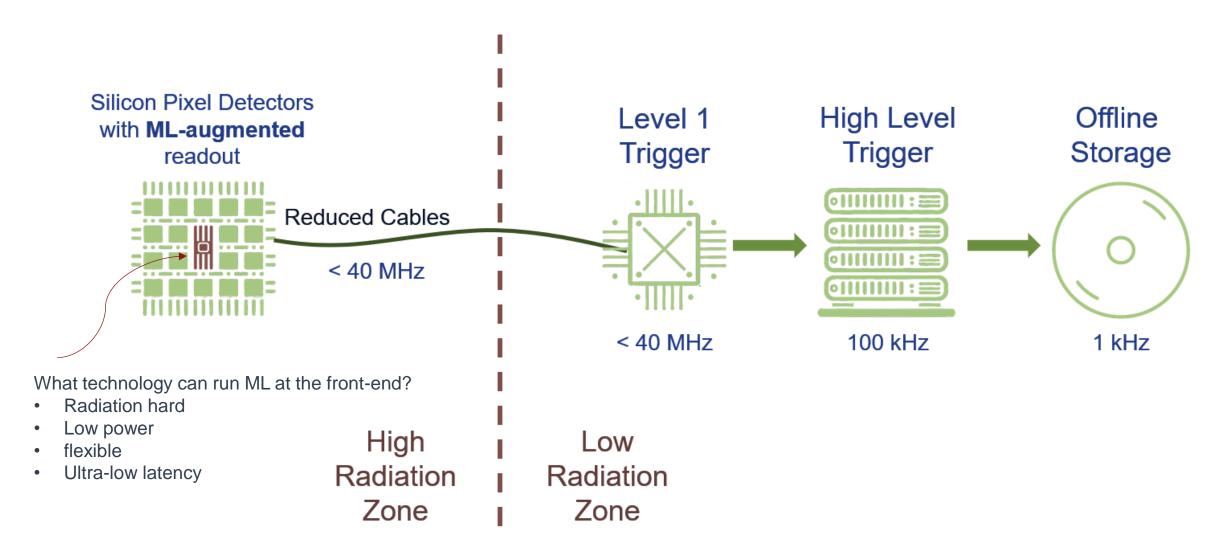

### ML-augmented readout system

### ML-augmented readout system

BOLD PEOPLE VISIONARY SCIENCE REAL IMPACT BOLD PEOPLE VISIONARY SCIENCE REAL IMPACT

2

### What's Embedded FPGA?

### Compute architectures

### Compute architectures

### Embedded FPGAs (eFPGAs)

Basic idea is that you can put reconfigurable logic in your ASIC design.

- Full reconfigurability: can be re-configured just like a regular FPGA

- Power Efficiency: ASIC implementation means lower power than FPGA ("best of both worlds")

- Development Time: "plug-and-play" FPGA fabric into ASIC

- Cost: no need for costly engineer hours or licenses to design an ML chip

Also, in use as hardware accelerators

# Open source (e)FPGA generators

Why they are included by default in Google's programs?

See <u>Larry Ruckman's (CPAD 2024)</u> talk for more

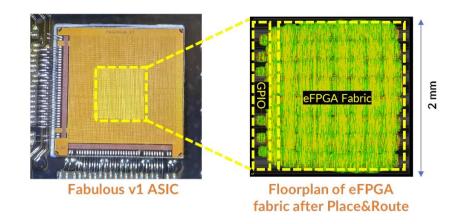

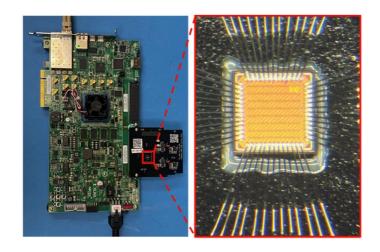

### eFPGA Development at SLAC

- SLAC's Technology Innovation Directorate (TID) demonstrated an eFPGA design in a 130nm CMOS Multi-Process Wafer (v0)

- Subsequently designed a version 1 "proof-of-concept" eFPGA in 28nm CMOS in 2023 (v1), 1mm x

1mm

Results are published on 2024 JINST 19 P08023

Both are designed with **open-source** framework "FABulous" from University of Manchester. **Low cost and barrier to entry for institutions to participate in microelectronics design.**

BOLD PEOPLE VISIONARY SCIENCE REAL IMPACT BOLD PEOPLE VISIONARY SCIENCE REAL IMPACT

3

### Machine Learning at the Front-End

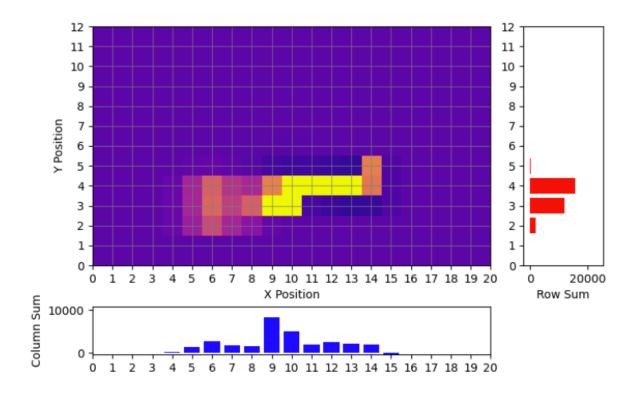

#### **Smart Pixel Dataset**

We used the Smart Pixel Dataset\*, which are pixel clusters produced by charged particles (pions) with real kinematics from CMS Run 2.

- 0.5 Millions of 20\*13\*21 (time

x y position x X position) 2D

"video" + y-local (y0)

- 13 truth info: positions, pT, angles...

Timestep: 4 | Data Point: 19 | pt: -0.23

<sup>\* &</sup>lt;a href="https://zenodo.org/records/7331128">https://zenodo.org/records/7331128</a>

### Proof-of-concept study

Reduce data rate by momentum classification using a **Boosted Decision Tree** with conifer.

Aconifer

### Proof-of-concept Results

We train a BDT to classify tracks with transverse momentum larger than 2 GeV, quantize and implement on the v1 eFPGA in 28nm CMOS. Use only 294 LUTs and nothing else (BRAM\_18K, DSP, FF, URAM). Latency under 25ns. Hardware test achieves 100% accuracy compared to expected output!

Published <u>2024 JINST **19** P08023</u>

#### Journal of Instrumentation

PAPER

Embedded FPGA developments in 130 nm and 28 nm CMOS for machine learning in particle detector readout

J. Gonski, A. Gupta, H. Jia, H. Kim, L. Rota, L. Ruckman, A. Dragone and R. Herbst Published 28 August 2024 • © 2024 IOP Publishing Ltd and Sissa Medialab. All rights, including for text and data mining, Al training, and similar technologies, are reserved.

Journal of Instrumentation, Volume 19, August 2024

Citation J. Gonski *et al* 2024 *JINST* **19** P08023

DOI 10.1088/1748-0221/19/08/P08023

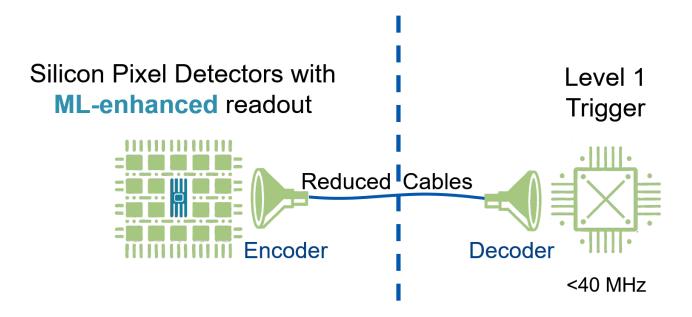

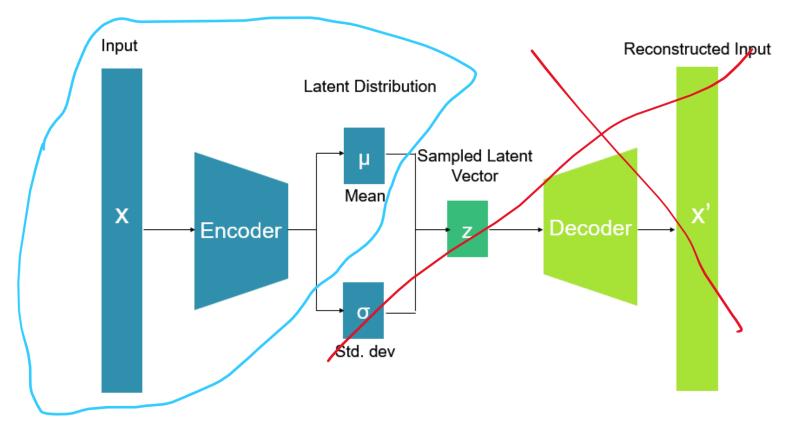

#### Variational Autoencoder for readout

Variational Autoencoder is a type of neural network which learns to compress and reconstruct input data. We propose to use them for off-detector data compression and anomaly detection for readout system.

- Latency constraint <25 ns</li>

- Within eFPGA limited resources

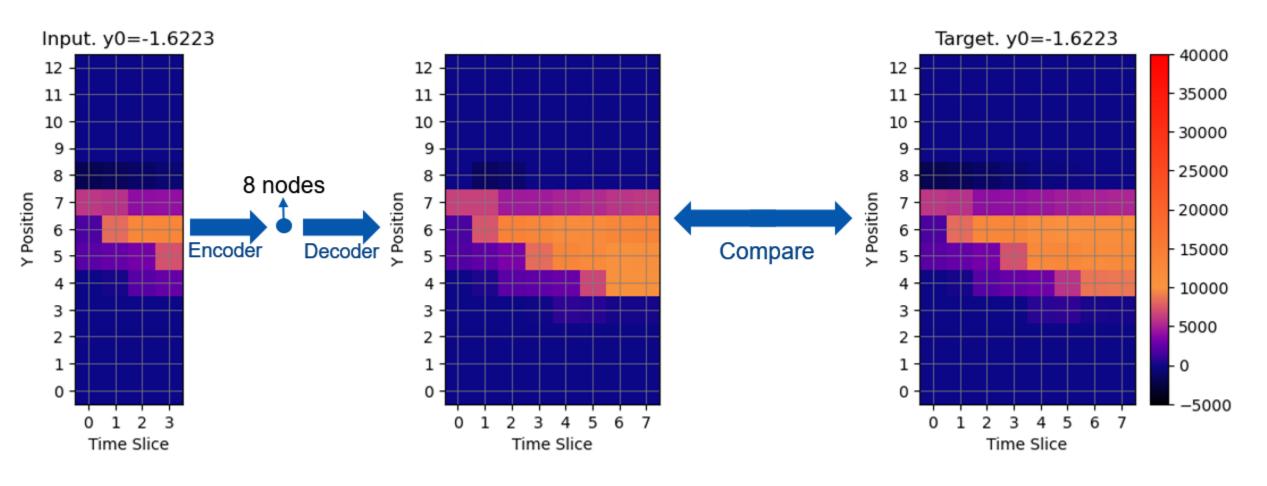

### **Example reconstruction**

The model learns to reconstruct the whole piece with only 4 time slices!

### Variational Autoencoder (VAE)

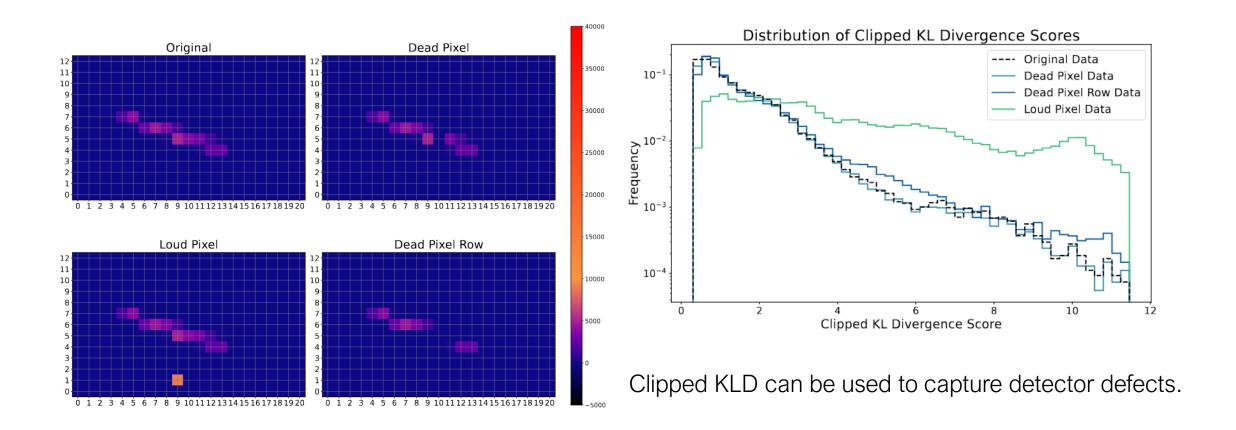

Kullback–Leibler divergence(KL) is a regularization term in training loss which helped shape the latent distribution into gaussian. Then the clipped KL divergence can be used as anomaly score with only the mean.

$$2 \cdot KL = \sum_{i} \mu_i^2 + \sigma_i^2 - \log \sigma_i^2$$

### VAE for Defect monitoring

Results on arXiv 2411.01118 and submitted to JHEP.

BOLD PEOPLE VISIONARY SCIENCE REAL IMPACT BOLD PEOPLE VISIONARY SCIENCE REAL IMPACT

4

## Conclusions and Next steps

### Conclusions and Next steps

- Real-time machine learning embedded directly in particle detector hardware could revolutionize how these instruments operate at future colliders.

- Highly generalizable: can apply to any input data format

- Applications under study: silicon trackers/calorimeters, drift chambers, dual readout, hardware accelerators, common electronics

- Expressions of interest submitted to CPAD RDC4 (electronics), FCC, US Higgs Factory

- Team: SLAC, LBNL, Baylor University, Fermilab, University of Hawaii, University of Michigan

- Future work (1-5 years):

- Tape out larger eFPGA for more complex algorithms, hardware verification, and power studies

- Implement radiation-hardness and/or cryogenic tolerance in open-source design frameworks

- Develop experiment-specific prototypes for Higgs factory & more

- Resources needed: Al-ASIC engineer design hours, physicist hours, M&S for tape outs

- Hope to deliver eFPGAs as a viable readout technology for future Higgs factory detector designs!