## SELECTIONAL ACCELERATOR LABORATORY

SLAC TID-AIR Technology Innovation Directorate Advanced Instrumentation for Research Division

R. Herbst

Deploying ML In Hardware FPGAs & ASICs

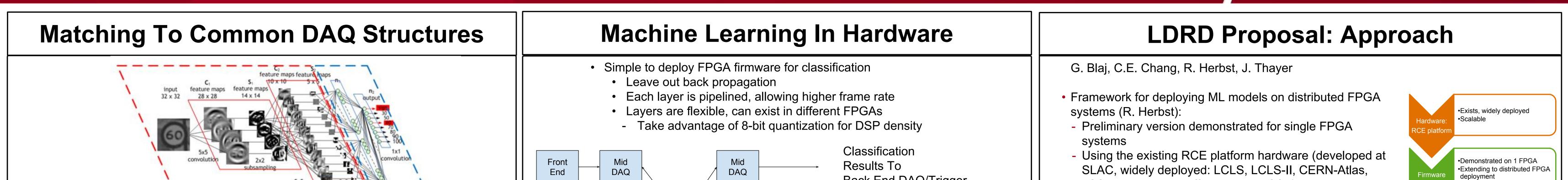

| 5x5<br>convolution subsampling convolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | End DAQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                        | nd DAQ/Trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LSST, Fermi Lab, Jefferson Lab, LSST)                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| feature extraction classification<br>Detector<br>Region FRGA FPGA<br>Detector<br>Region Conv Conv Full<br>FPGA FPGA FPGA<br>FPGA FPGA FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Front Mid DAQ<br>Front Mid DAQ<br>Front End DAQ<br>Front Mid DAQ<br>Front Mid DAQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Mid<br>DAQ<br>Mid<br>DAQ<br>Mid<br>DAQ<br>Mid<br>DAQ<br>Mid<br>DAQ<br>Mid<br>DAQ<br>Mid<br>DAQ<br>Mid<br>DAQ<br>• First few laye<br>of data (conve<br>• Inter-FPGA c<br>- Inter-firmwa<br>• Shared hyb | ates need to event build<br>poses<br>rs have minimal overlap<br>olution)<br>onnections overlap data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>ML based algorithms for reducing and summarizing data from 2D detectors (G. Blaj):</li> <li>Preliminary version matches performance of 'classical' algorithms with 1-2 orders of magnitude speed up</li> <li>Sequence of hand-crafted filters (based on convolutional networks with optimized architectures)</li> <li>Bonus: each layer, each node have clear physical meaning</li> <li>Co-development with firmware framework and optimization (conversion to integers, pruning)</li> </ul> |

| Proposed ML Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ML Frar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ML Framework Proof Of Concept                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <ul> <li>Training deep learning models for data summarization, event<br/>vetoing (CE. Chang, scientists) using existing data and<br/>standard GPU training</li> </ul>                                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>Xilinx tool flow is geared towards co-processor based machine learning         <ul> <li>Possible some openCl design flows allow self contained classification system</li> <li>Proper solution allows the deployed networks to be integrated into a layere system</li> </ul> </li> <li>Working design flow for deploying neural networks in FPGA auto generated from Caffe model:         <ul> <li>Train &amp; Test Data Sets</li> <li>Caffe prototxt file</li> <li>Caffe train and test software (GPU or FPGA accelerated)</li> </ul> </li> </ul>                                                                                                                                                                                                                        | <pre>rmware Library SURF aclab/surf en decimal recognition) Example: ConfigArray(5 downto 0) := ( &gt; 1, strideY =&gt; 1, SizeY =&gt; 5, =&gt; 0, n =&gt; false), 2, strideY =&gt; 2, kernSizeX =&gt; 2, kernSizeY =&gt; 2), &gt; 1, strideY =&gt; 1, SizeY =&gt; 5, =&gt; 0,</pre>                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                        | <ul> <li>Performance optimization and validation with existing application-specific LCLS data sets (J. Thayer, scientists): <ul> <li>Applications: single particle imaging, diffuse scattering, protein crystallography, etc.</li> </ul> </li> <li>Will enable: <ul> <li>Real time summarization (online AMI), compression</li> <li>Automatic event vetoing, tuning of experiment parameters</li> </ul> </li> <li>Risks: limited <ul> <li>Existing hardware: PCI-Express based FPGAs, scalable RCE platform, natively supporting LCLS and LCLS-II DAQ</li> <li>Preliminary version of firmware framework for ML model</li> </ul> </li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VHDL config record<br>derived directly from<br>prototxt file (python)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | chanCnt => 50, rectEn => false),<br>3 => genCnnPoolLayer (strideX => 2, strideY => 2, kernSizeX => 2, kernSizeY => 2),<br>4 => genCnnFullLayer ( numOutputs => 500, chanCnt => 50, rectEn => true ),<br>5 => genCnnFullLayer ( numOutputs => 10, chanCnt => 1, rectEn => false ));                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | deployment demonstrated for single FPGAs <ul> <li>Preliminary version of low-level algorithms demonstrated</li> <li>Application-specific LCLS data sets already exist</li> </ul>                                                                                                                                                                                                                                                                                                                      |

| Approaches To ML In Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | les I o ML in Hardware Existing F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                        | IID-AIR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ESPCI-Express Application Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <ul> <li>Four categories of approaches to ML in FPGAs * <ul> <li>Single processing engine</li> <li>Systolic array, processing each layer sequentially</li> <li>Software based processing with FPGA coprocessor</li> </ul> </li> <li>Streaming architecture <ul> <li>One processing engine per network layer</li> <li>Synchronous dataflow (SDF) model for mapping CNNs to FPGAs</li> <li>Often involving software coordination, but not necessary</li> <li>Vector processor</li> <li>Instructions specific to accelerating the operations of convolutions</li> <li>Software driven processing with FPGA coprocessor</li> </ul> </li> <li>Neurosynaptic processor</li> <li>Map digital neurons and their interconnecting weights</li> <li>ASIC based processing engines</li> </ul> | <ul> <li>The following frameworks are being studied to see if they can be used or serve as a guide for a SLAC framework</li> <li>Xilinx: FINN <ul> <li>Open Source</li> <li>Xilinx Vivado HLS</li> <li>Binarized Neural Networks (BNNs)</li> <li>https://github.com/Xilinx/FINN</li> </ul> </li> <li>CERN, Columbia, Fermilan, MIT, UI, etc: hls4ml <ul> <li>Open Source</li> <li>Xilinx Vivado HLS</li> <li>Demonstrated streaming inference with small networks</li> <li>https://hls-fpga-machine-learning.github.io/hls4ml/</li> </ul> </li> </ul> |                                                                                                                                                                                                        | <ul> <li>↓QSFP[0]:TX[3:0]<br/>QSFP[0]:RX[3:0]<br/>QSFP[0]:156.25MHz<br/>QSFP[0]:125MHz</li> <li>156.25MHz UserClock</li> <li>↓QSFP[1]:TX[3:0]<br/>QSFP[1]:RX[3:0]<br/>QSFP[1]:156.25MHz<br/>QSFP[1]:125MHz</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                        | Partial<br>Reconfiguration<br>Application<br>AXI[3:0] 128-bit<br>250MHz<br>AXI<br>AXI<br>AXI<br>AXI<br>AXI<br>AXI<br>AXI<br>AXI                                                                                                                                                                                                                                                                                                                                                                       |

| <ul> <li>FPGA based solutions tend to fall into the "Streaming architecture" or<br/>"vector processor" categories</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ul> <li>Imperial College London: fpgaConvNet         <ul> <li>Source Not Available</li> <li>Xilinx Vivado HLS</li> <li><u>http://cas.ee.ic.ac.uk/people/sv1310/fpgaConvNet.html</u></li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                        | <ul> <li>Also provides</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | dard application interfaces which are portable between hardware platforms<br>LCLS1 and LCLS2 timing cores along with timing/data event builder blocks<br>version of Amazon Cloud Computing node, static support blocks with user                                                                                                                                                                                                                                                                      |

| * arXiv:1612.07119 [cs.CV]: "FINN: A Framework for Fast, Scalable Binarized Neural<br>Network Inference"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                        | defined partial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I reconfiguration core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| The RCE Platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Commercial Xilinx Hardware                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

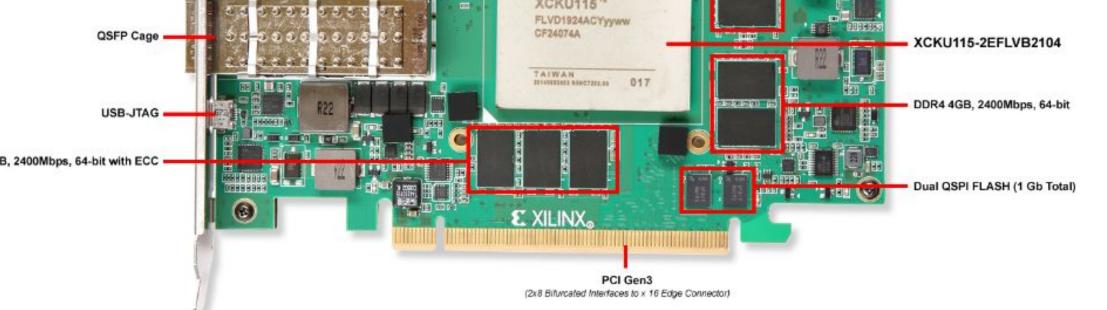

| <ul> <li>High performance platform with 9 clustered processing elements (SOC)</li> <li>Dual core ARM A-9 processor</li> <li>1GB DDR3 memory</li> <li>Large FPGA fabric with numerous DSP processing elements</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Xilinx KCU1500 co-processor<br>• XCKU115 FPGA<br>• 2 QSFP optical module<br>• 16GB DDR<br>• Amazon AWS<br>Xilinx Virtex UltraScale+ VCU                                                                                                                                                                                                                                                                                                                                                                                                               | S                                                                                                                                                                                                      | DR4 4GB, 2400Mbps, 64-bit with ECC JTG-PC4 Header                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Data processing daughter board with dual Zynq 7045 FPGAs 12 bi-direction HS links between each FPGA and the RTM

> Front panel Ethernet 2 x 4, 10-GE SFP+

## Numerous experiments

- LSST

- Heavy Photon Search, LDMX

- DUNE 35Ton / ProtoDUNE

- ATLAS Muon

- ITK Development

- nEXO (Baseline)

On board 40G Ethernet switch with 10G to each processing FPGA Supports 15 slot full mesh backplane interconnect!

Micro USB P

- SOC platform combines stable base firmware / software with application specific cores

- HLS for C++ based algorithms & compression

- Matlab for RF processing

3/4 Length, Full Height PCIe Form Factor

PCIe Edge Connect Gen3 x16, Gen4 x8

XCVU9P-L2FSGD2104E

21 000 0000 CIM 0000 IT 1 0 00 0

Quad 16GB DDR4 DIM (64GB Total)

5, III 88 Saa 8 III

PCIe Aux Power Connector