November 7<sup>th</sup>, 2024

# **4D Tracking Electronics Developments @ SLAC**

**Bojan Markovic – TID ID Integrated Circuits, SLAC National Accelerator Laboratory (***markovic@slac.stanford.edu***)** on behalf of SLAC's TID and FPD

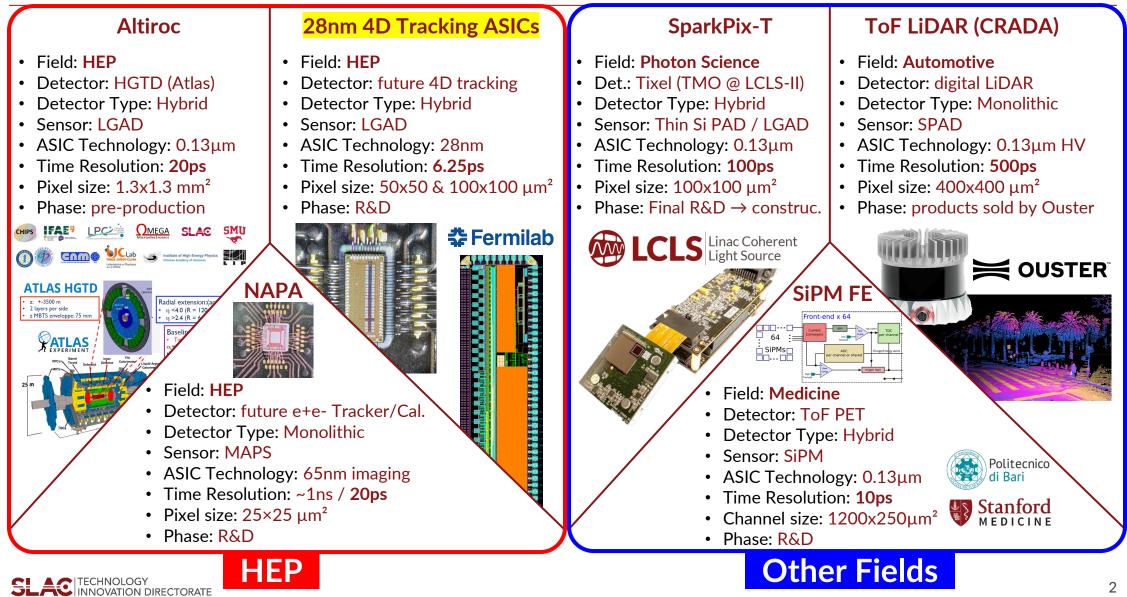

### Timing ASICs @ SLAC

workshop 2024

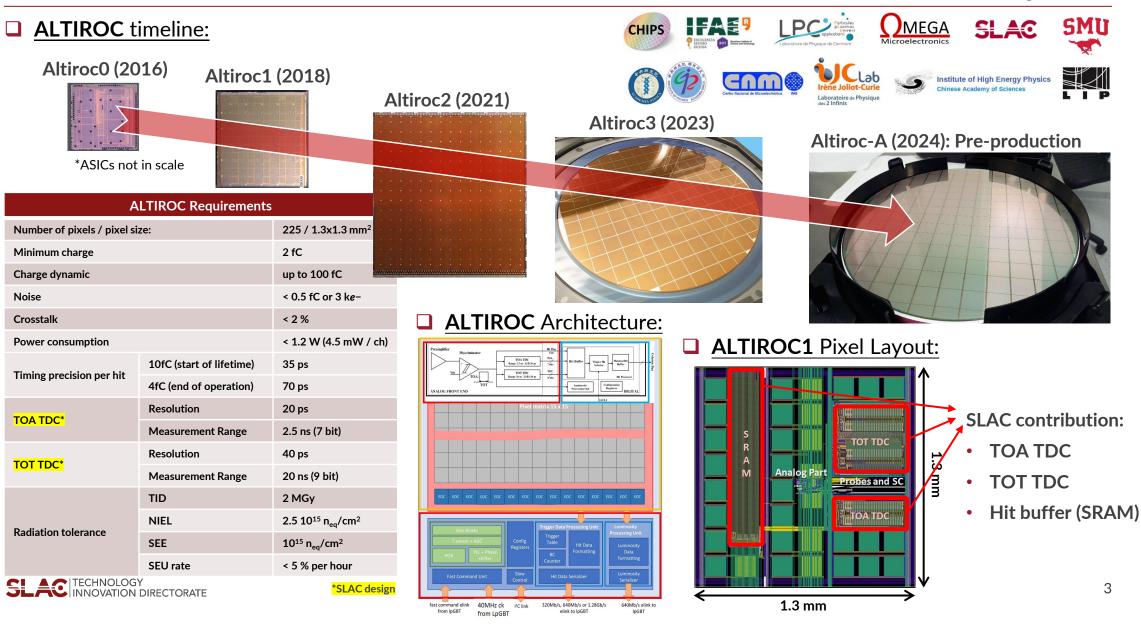

### ATLAS HGTD: ALTIROC ASIC (130nm)

4<sup>©</sup>Tracking workshop 2024

### TJ 65nm imaging process work

#### 4<sup>®</sup>Tracking workshop 2024

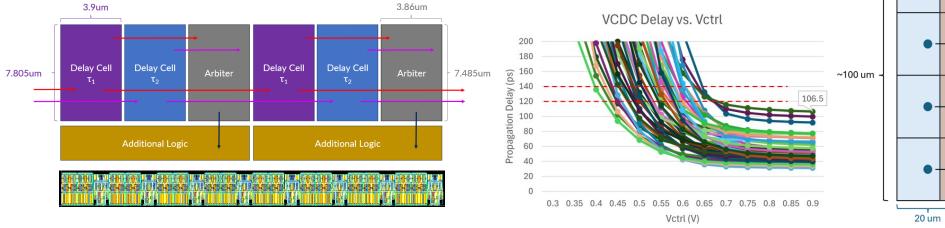

#### NAPA: NAnosecond Pixel for large Area sensors:

- Goal: achieve low-power, large-area, ultra-low-mass detector with ~ns timing

- Long term application: Trackers/ Calorimeters in future e+e- colliders

- Designed in Tower Semiconductor 65 nm imaging technology, capitalizing on the CERN WP1.2 efforts over a decade of sensor optimization

#### Exploring the possibility of incorporating a 20ps TDC:

- Work by Megan Zeng, Sanford University PhD. student (HEPIC summer internship)

- Design of the TDC core complete

Pixel

## Designs in 28nm

#### DOE HEP Detector R&D program

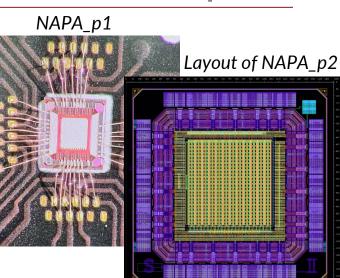

v1 (submitted Jan. 2023) wire-bounding issues

v2 (submitted Jan. 2024, received Jun. 2024) – testbench characterized

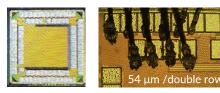

#### 28nm TDC ASIC: 4 channels, each with 50ps and 6.25ps sections

Further efforts (Victor Turbiner, Stanford U. PhD. student):

- delay line devices for CFD implementation

- clustering algorithms

DOE Accelerate Innovations in Emerging Technologies

3D Integrated Sensing Solutions – SLAC, FNAL, LLNL

SLAC #Fermilab

Parallel effort to the development and fabrication of LGADs on 12" wafers in partnership with Tower Semiconductor

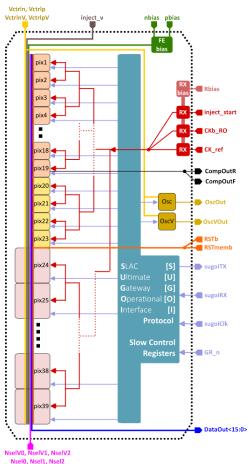

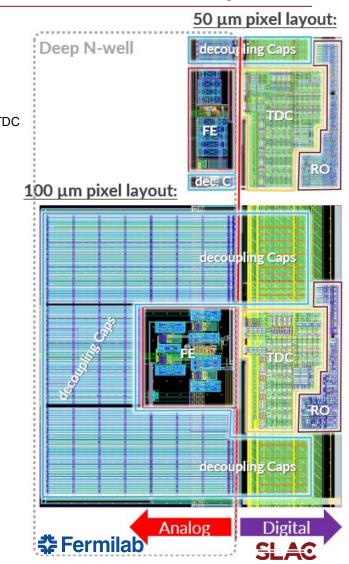

The first LGAD readout prototype (1x3mm<sup>2</sup>) submitted in Aug., testing to start in Dec. 2024.

- Linear pixel array (39 pixels); 2 variants of 50µm and 1 variant of 100µm size pixels;

- Pixels include analog frontend and TDC for TOA and TOT;

- Sparsified readout scheme.

Next summer, we will tape-out a MPW run (5x6mm<sup>2</sup>) with 50x50 100 $\mu$ m and/or 100x100 50 $\mu$ m pixel array.

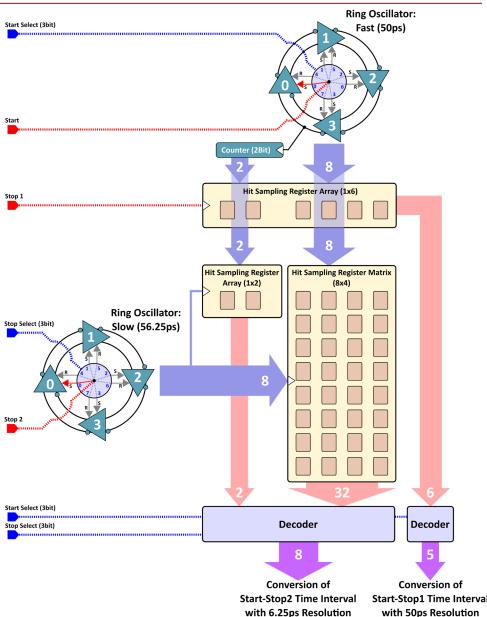

### 28nm TDC: Architecture

- 2D Vernier Architecture:

- Fast Ring Oscillator with 50ps propagation delay cells;

- Slow Ring Oscillator with 56.25ps propagation delay cells;

- START + two STOP signal for simultaneous time-of-arrival (TOA) and time-over-threshold (TOT) measurements;

- Start-Stop1 Coarse time resolution (TOT): 50ps;

- Start-Stop2 Fine time resolution (TOA): 56.25ps 50ps = 6.25ps;

- Sliding scale technique for improvement of conversion linearity:

- Both ring oscillators have programable starting conditions via delay cell set/reset function;

- Starting conditions randomly selected each measurement cycle and corresponding values subtracted from the conversion result;

- Same time intervals converted with different parts/bins of the TDC conversion characteristics;

- Sliding scale transforms the non-linearities into stochastic variable thus effectively improving the conversion linearity at the expense of worsening single-shoot precision.

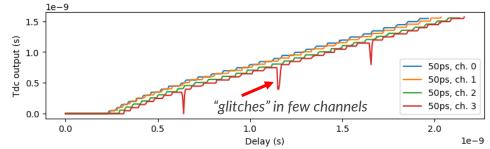

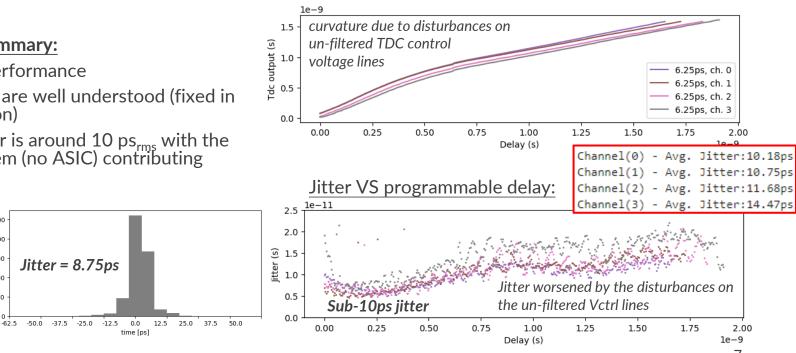

### 28nm TDC: Characterization

#### TDC prototype ASIC test setup: **Characterization summary:** Overall good performance Few issues that are well understood (fixed in the next iteration) Full system jitter is around 10 $\ensuremath{\mathsf{ps}_{\mathsf{rms}}}$ with the test board system (no ASIC) contributing around 6 ps<sub>rms</sub>

25000

20000

15000

5000

5 10000

Jitter = 8.75ps

time [ps]

#### 50ps (TOT) TDC Output VS programmable delay:

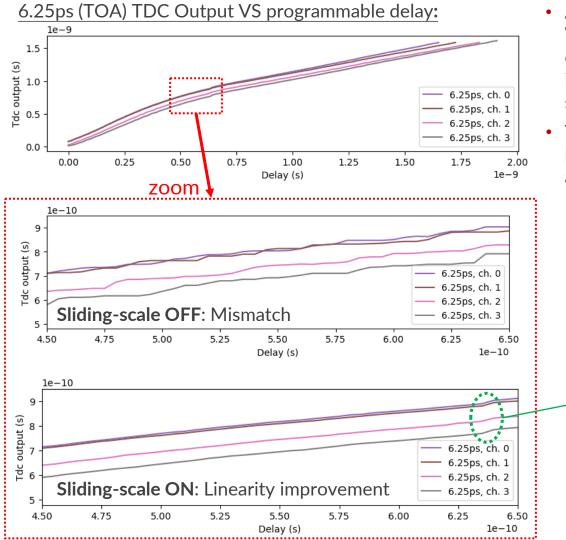

#### 6.25ps (TOA) TDC Output VS programmable delay:

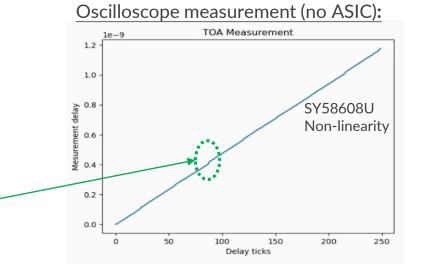

### 28nm TDC: Sliding-Scale Linearity Improvement

Achieving sub-10ps resolution in all PVT conditions requires Vernier architecture (LSB given by the difference of propagation delays) that suffers heavily from mismatch (especially true for implementations that target small pixel sizes) resulting in significant non-linearities of the TDC characteristics.

racking

workshop 2024

The developed TDC implement the sliding-scale technique <sup>[1,2]</sup> for linearity improvement to mitigate the weakness of the Vernier approach.

#### [1] C. Cottini, **E. Gatti**, and V. Svelto, "A new method for analog to digital conversion," Nucl. Instr. Meth., vol. 24, p. 241, Aug. 1963.

[2] **E. Gatti**, P. F. Manfredi, and D. Marino, "Analysis and characterization of cyclic-scale compensated analog-to-digital converters," Nucl. Instrum. Methods, vol. 165, no. 2, pp. 225–230, Oct. 1979.

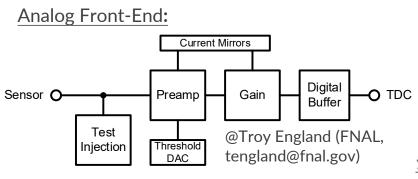

### 3D Integrated Sensing Solutions: FE ASIC

4<sup>®</sup>Tracking workshop 2024

| Frontend Specification              | Value                                     |  |  |  |

|-------------------------------------|-------------------------------------------|--|--|--|

| Total Power Density                 | $1 W/cm^2$                                |  |  |  |

| Power 50x50 $\mu$ m <sup>2</sup>    | 25 μW                                     |  |  |  |

| Time of Arrival (ToA) Jitter (ASIC) | <b>10</b> <i>ps</i> <sub><i>rms</i></sub> |  |  |  |

| Min Signal for ToA Jitter           | 1.3 <i>fC</i>                             |  |  |  |

| Max Signal                          | 13 <i>fC</i>                              |  |  |  |

| Dynamic Range                       | 10 - 20                                   |  |  |  |

| Repetition Rate at each Pixel       | 100 <i>kHz</i>                            |  |  |  |

| LGAD Input Cap. Approx.             | $11.52  aF/\mu m^2$                       |  |  |  |

1<sup>st</sup> prototype submitted Aug. 2024, characterization to start Dec. 2024

|                   | TDC metrics                                                 |  |  |  |

|-------------------|-------------------------------------------------------------|--|--|--|

| Technology        | 28nm                                                        |  |  |  |

| Timing resolution | 6.25ps (TOA) / 50ps (TOT)                                   |  |  |  |

| Time depth        | <del>1.6ns (8bit / 5bit)</del> <b>12.8ns (11bit / 8bit)</b> |  |  |  |

|                   | easily extendable by simple addition of bits to the counter |  |  |  |

| TDC area          | <b>26μm x 40.5μm</b> (1.7μm x 13.3μm per additional bit)    |  |  |  |

| Power consumption | (average, 25ns conversion cycle / bunch crossing)           |  |  |  |

| 10% occupancy     | <del>16μ₩</del> 51.1μW                                      |  |  |  |

| 1% occupancy      | <del>2.5μ₩</del> 6.2μ₩                                      |  |  |  |

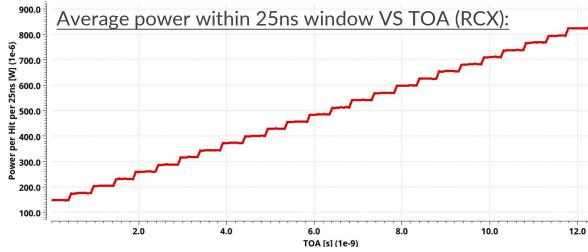

### 3D Integrated Sensing Solutions: FE ASIC Power

TDC idle consumption (due to leakage): ~1.2μW

**TDC** power consumption depends on time-interval being measured

• For uniformly distributed time-intervals *Ti* the average power consumption per Hit in a 25ns measurement window is:

$$P_{\frac{av}{hit}/T_{CK}} = 500 \mu W$$

Average power consumption:

$$P_{av} = 1.2\mu W \cdot (1 - Occupancy) + P_{\frac{av}{hit}/T_{CK}} \cdot Occupancy$$

- For 10% occupancy: ~ 51.1μW

- For 1% occupancy: ~ 6.2μW

|          |           | Power Consumption (average, 40MHz clock ) [ $\mu$ W] |      |               |      |                       |      |               |       |  |

|----------|-----------|------------------------------------------------------|------|---------------|------|-----------------------|------|---------------|-------|--|

| 80<br>90 |           | 50 μm x 50 μm pixel                                  |      |               |      | 100 μm x 100 μm pixel |      |               |       |  |

| 8        | Occupancy | FE                                                   | TDC  | *Clk<br>three | Tot. | FE                    | TDC  | *Clk<br>three | Tot.  |  |

|          | 0%        | 11.6                                                 | 1.2  | 1.2           | 14   | 81                    | 1.2  | 2.4           | 84.6  |  |

|          | 1%        | 11.6                                                 | 6.2  | 1.2           | 19   | 81                    | 6.2  | 2.4           | 89.6  |  |

| -1       | 2%        | 11.6                                                 | 11.2 | 1.2           | 24   | 81                    | 11.2 | 2.4           | 94.6  |  |

|          | 4%        | 11.6                                                 | 21.2 | 1.2           | 34   | 81                    | 21.2 | 2.4           | 104.6 |  |

|          | 6%        | 11.6                                                 | 31.1 | 1.2           | 43.9 | 81                    | 31.1 | 2.4           | 114.5 |  |

|          | 8%        | 11.6                                                 | 41.1 | 1.2           | 53.9 | 81                    | 41.1 | 2.4           | 124.5 |  |

|          | 10%       | 11.6                                                 | 51.1 | 1.2           | 63.9 | 81                    | 51.1 | 2.4           | 134.5 |  |

\*Clock distribution contribution is derived assuming hierarchical tree on a matrix of 256x256 50µm pixels and 128x128 100µm pixels (parasitic extracted sim.)