####

#### **Superconducting Parametric Amplifier Design**

Kyle Woodworth, Chandrashekhar Gaikwad, Davide Braga, Kater Murch, Farah Fahim

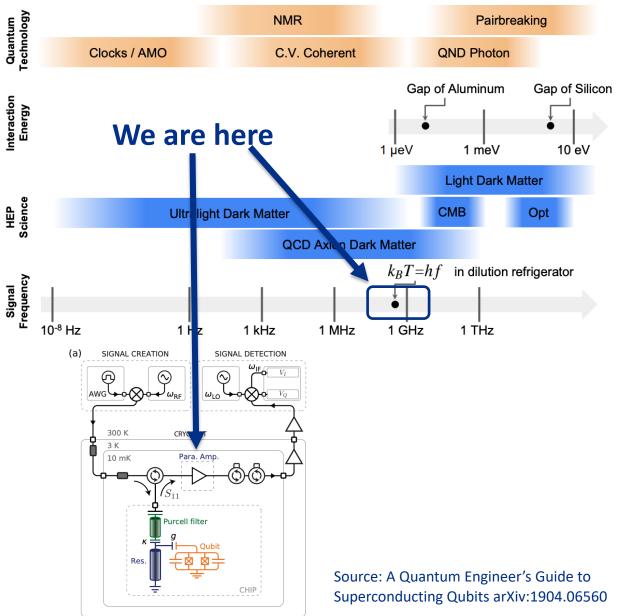

#### Source: QIS for HEP report arXiv:2311.01930

#### Why Parametric Amplifiers

- HEP and QIS

- RDC8 and RDC4

- Cryogenic temperature

operation

- High Quantum Efficiency

- General Purposed Quantum readout chains

#### **Parametric Amplifiers At Fermilab**

- Tape-out: March of 2023

- Fab: MIT-LL SFQ5ee [100 uA/um<sup>2</sup>; 8 Nb Layers]

- Established and matured superconducting JJ process

- Repeatable and well controlled for ASIC applications

- Frequent MPW runs

- Chip Contents

- 2 JPA experiments

- 2 JTWPA experiments

- Test Structures

- Estimated delivery: Late November 2023

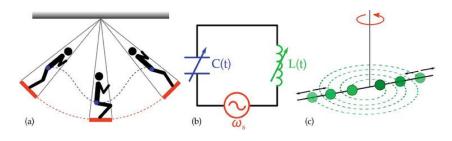

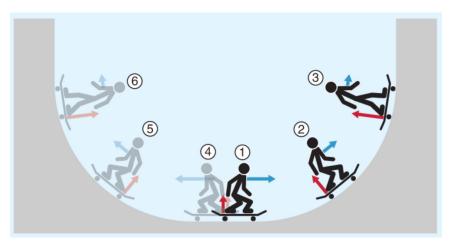

#### What is a Parametric Amplifier?

- RF Mixer combined with amplifier

- Parametric refers to the process of modulating a parameter of a system of equations

- Signal tone is mixed with pump tone via non-linearity

- Energy from pump is converted into signal photons

- Akin to being pushed on a swing or skating in a half pipe

Source: Superconducting Josephson-Based Metamaterials for Quantum-Limited Parametric Amplification: A Review

Source: Superconducting Parametric Amplifiers: The State of the Art in Josephson Parametric Amplifiers DOI:10.1109/MMM.2020.2993476

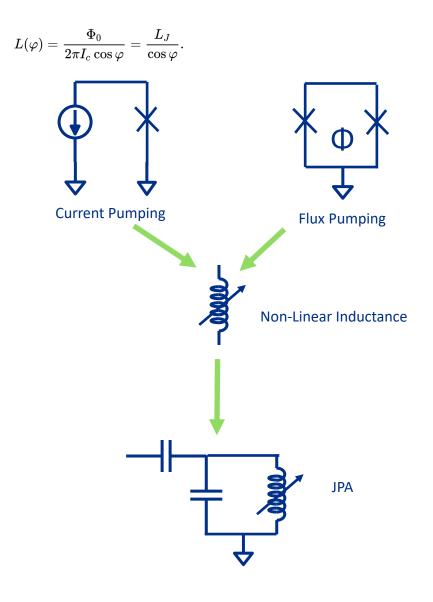

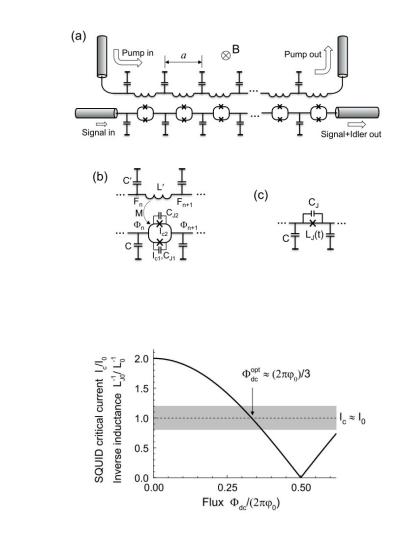

# **Josephson Parametric Amplifier**

- Increasing current through JJ increases the effective inductance

- Single JJ/JJ Chain = Current Pumping via modulation of the Josephson Inductance

- DC SQUID = Flux Pumping via modulation of the effective Ic of the SQUID

- 1 Port System

- Active termination

- Very small bandwidths

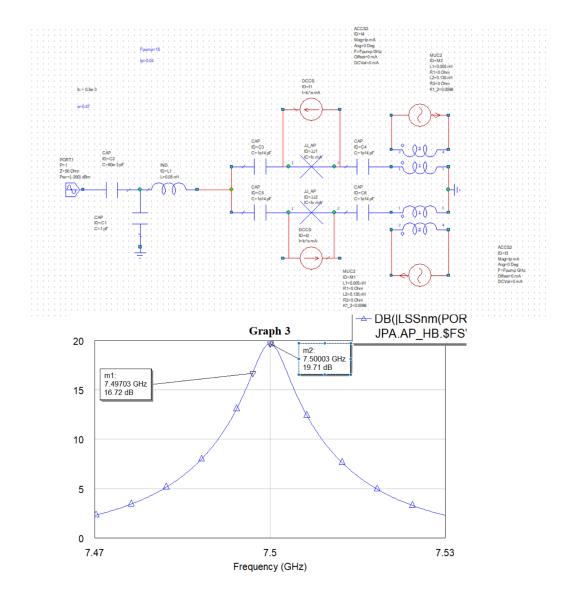

# **JPA Circuit Simulation**

- 2 different versions of JPA

- Crossed loop (0-effective area)

- No-crossed loop

- Original design adapted from original work by WashU collaborators

- ADMX and BREAD

- Specifications

- Coupling capacitance = 60fF

- Signal Frequency = 7.5 GHz

- Pump frequency = 15GHz

- Pump Amplitude = 40uA

- Gain = 20dB

- Bandwidth = 60MHz

- Tunable Bandwidth = <1GHz

Original Theory/Designs

https://arxiv.org/pdf/0808.1386.pdf

https://www.epj-conferences.org/articles/epjconf/pdf/2019/03/epjconf\_qtech2018\_00008.pdf

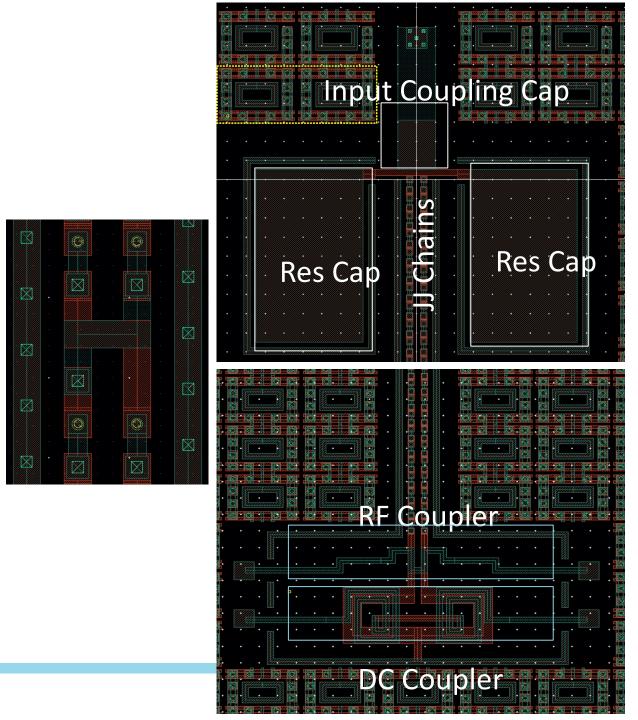

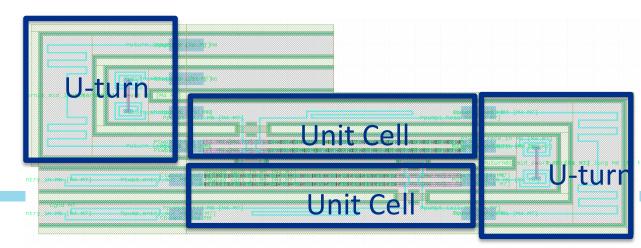

# **JPA Circuit Layout**

- SFQ5ee

- Original work was done with 1 layer

- RF Coupler = 0.5pH

- Minimizing capacitance between RF bias line and SQUID is essential for avoiding current pumping

- DC Coupler = 3pH

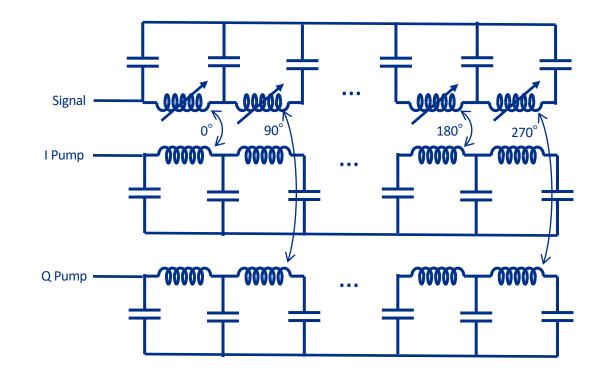

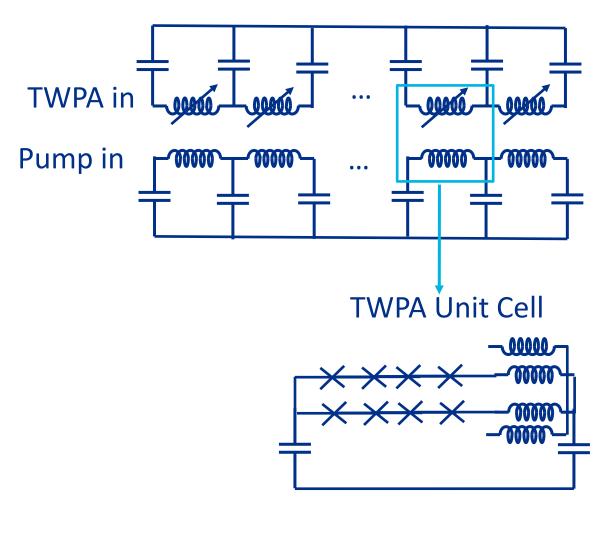

# What is a TWPA?

- AKA: JTWPA or Josephson Traveling Wave Parametric Amplifier

- A non-linear transmission line

- Phase matching (L-C's match)

- Current and Flux Pumping

- Much larger instantaneous bandwidth

- Floquet, SNAIL

- Theory first developed by Zorin 2019

- https://arxiv.org/pdf/1804.09109.pdf

# **Dispersion Engineering**

- Solutions

- Introducing stop-bands

- Varying size of JJ's along path

- Two parallel transmission lines

- Pump Tone

- Signal Tone

- Optimally bias TWPA for maximum slope of SQUID critical current

https://arxiv.org/pdf/1804.09109.pdf

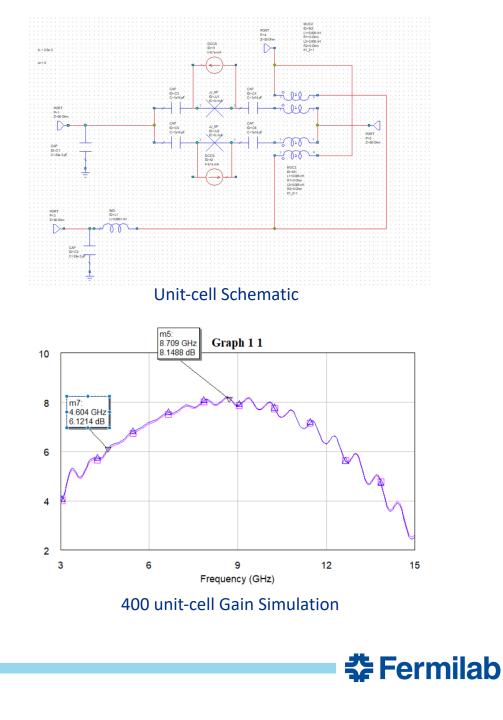

# **JTWPA Circuit Simulation**

- 400x and 800x unit-cell experiments

- Dispersion/impedance engineering

- Lumped element pump line matched to operating impedance of TWPA unit cells

- Specifications (400 unit cells)

- Pump frequency = 20GHz

- Pump Amplitude = 40uA

- Gain = 8dB @ 9GHz

- Bandwidth = 8GHz

# **Testing**

- Chips to be delivered End of November 2023

- Start testing mid-December

- Need fridge time to properly characterize noise performance, gain, and bandwidth

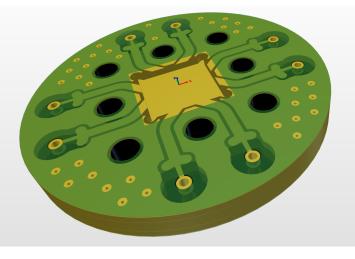

- Developing PCB for chip to bond

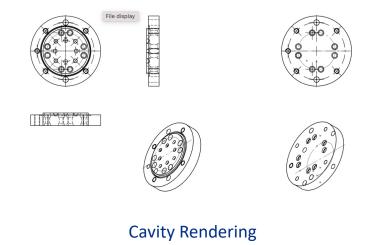

- Developing cavity to house PCB

PCB Rendering

#### **Future Work**

- 1000x and 2000x unit cells

- Mutually coupling RF clock phase as a dispersion matching technique which can increase tunable bandwidth

- Verify against open-sourced simulation tools

- Lower critical current density fabrication

- Shrinks SQUID loops

- Reduces the number of junctions required

- Increases beta