# CMS High Granularity Calorimeter ECON-D ASIC overview and radiation testing results

**FNAL/LPC:** Jyoti Babbar (Panjab) Bhim Bam (Alabama), Davide Braga, Alex Campbell (Alabama), <u>Grace Cummings</u>, Cristinel Gingu, Mike Hammer (Argonne), James Hirschauer, James Hoff, Neha Kharwadkar, Pam Klabbers, Danny Noonan, Paul Rubinov, Alpana Shenai, Cristina Mantilla Suarez, Chinar Syal, Xiaoran Wang, Ralph Wickwire. **FESB/Split:** Duke Coko. **CERN:** Gianmario Bergamin, Davide Ceresa, Rui De Oliveira Francisco, Szymon Kulis, Pedro Leitao, Matteo Lupi, Paulo Moreira, Simone Scarfi'. **Baylor:** Jon Wilson. **SMU:** Di Guo, Datau Gong, Dongxu Yang, Jingbo Ye. **KUL:** Bram Feas, Paul Jozef Leroux, Jeffery Prinzie.

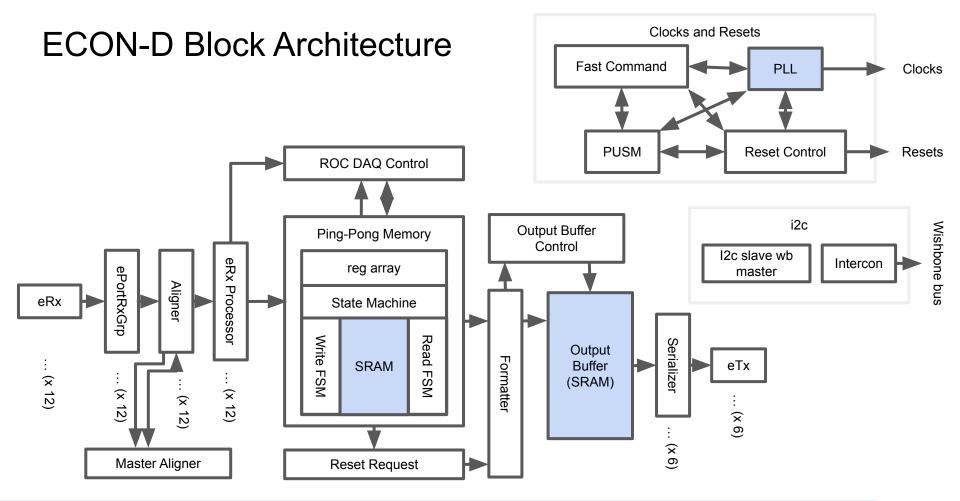

## Overview

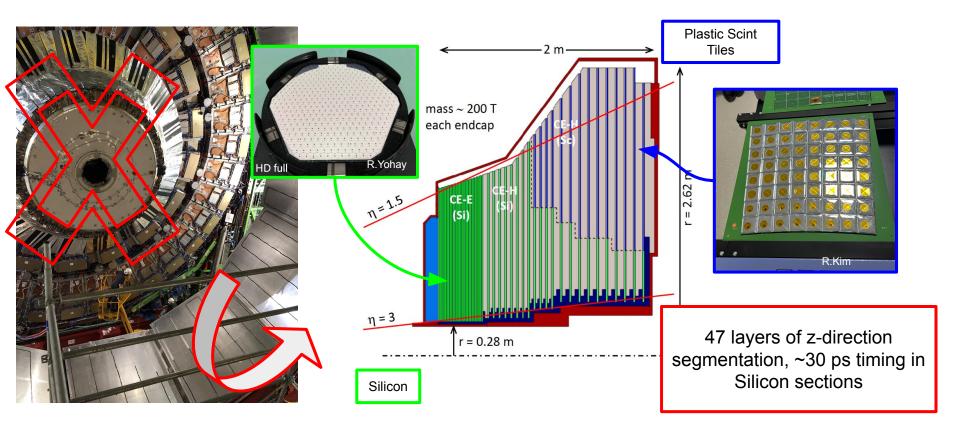

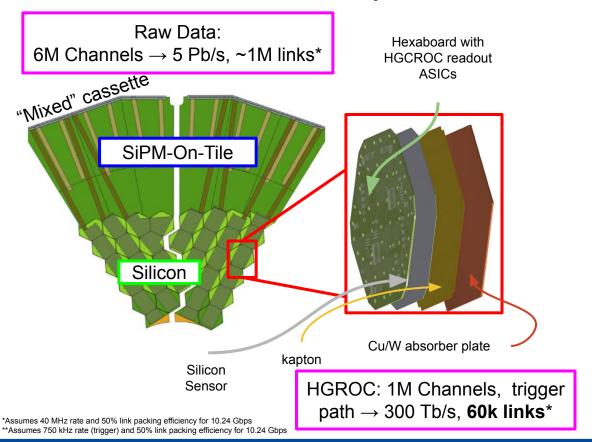

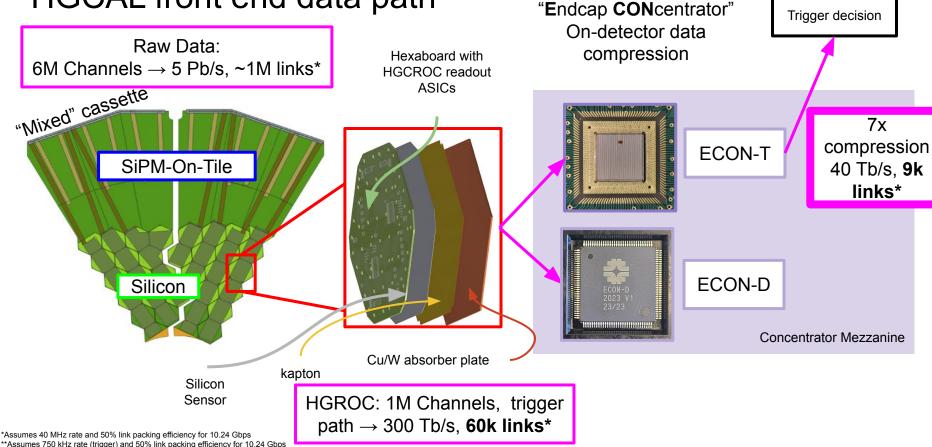

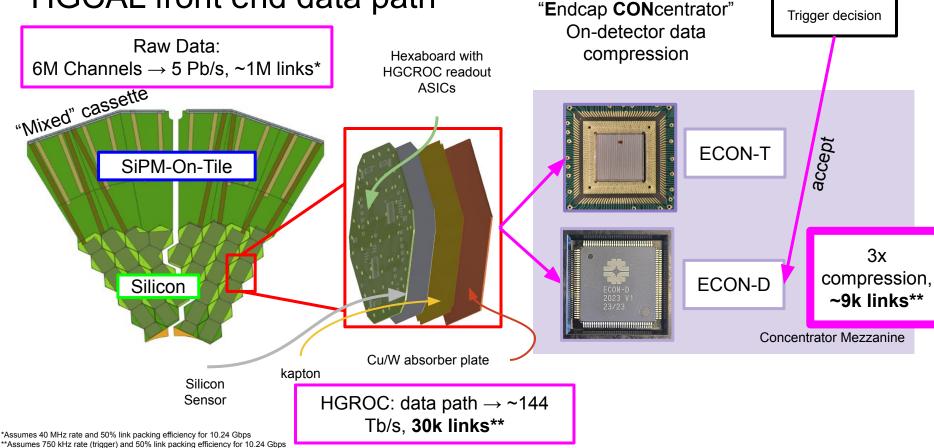

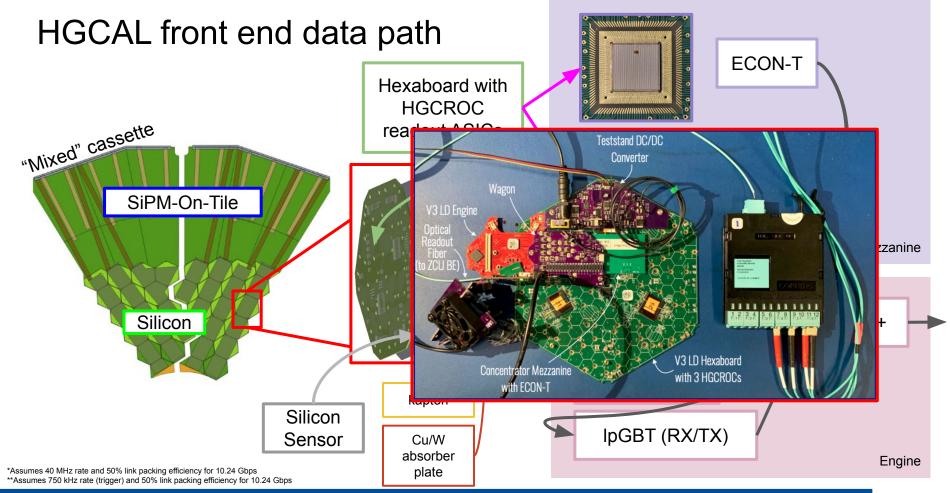

## CMS High Granularity Calorimeter Endcap, HL-LHC

Raw Data: 6M Channels → 5 Pb/s, ~1M links\*

\*Assumes 40 MHz rate and 50% link packing efficiency for 10.24 Gbps

\*\*Assumes 750 kHz rate (trigger) and 50% link packing efficiency for 10.24 Gbps

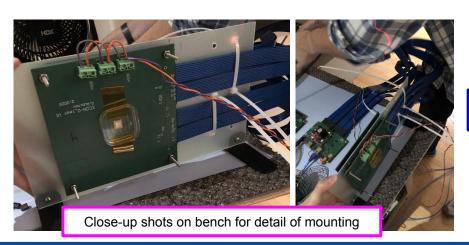

Measured with proton beam from the Northwestern Medicine Proton Therapy Center

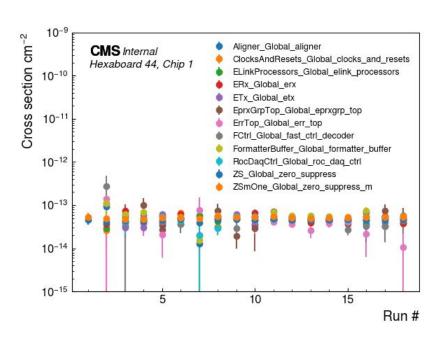

## Single Event Effect Testing

#### Goals of Single Event Effect (SEE) Test

- 1. Set *limit* on cross section (xs) requiring a reset

- All configuration registers triplicated did not expect to observe any errors

- 2. Confirm zero observed errors in triplicated i2c/config registers

- 3. Measure Single Event Upset (SEU) xs per bit for pre-voted flip-flop (FF)

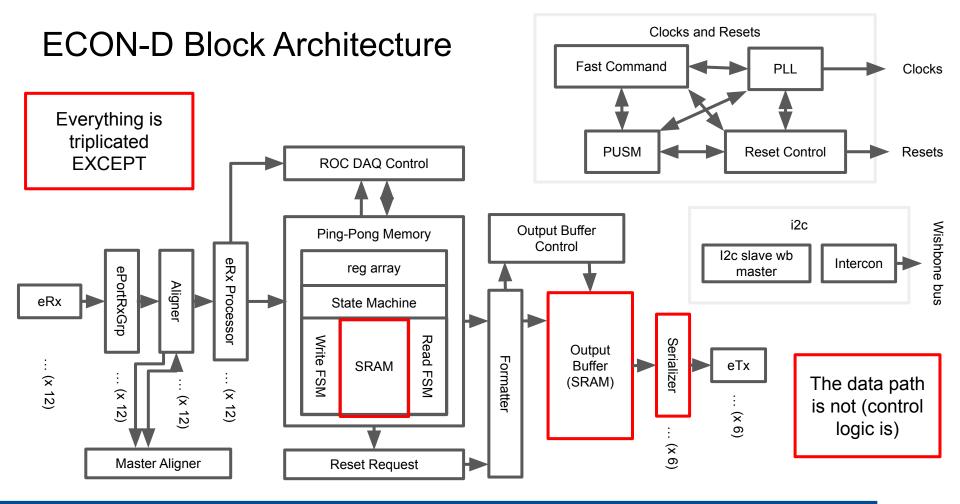

- Use TMR (triple modular redundancy) error counters

- Count of corrections

- Measure SEU-induced bit error rate in data

- Tests the serializer/deserialzer + SRAMs

- Errors in deserializer and SRAM only visible in triggered-data

- Serializer errors appear in IDLES

Total Fluence: 4.99E13 protons/cm2

#### Goals of SEE Test

- 1. Set *limit* on cross section (xs) requiring a reset

- All configuration registers triplicated did not expect to observe any errors

- 2. Confirm zero observed errors in triplicated i2c/config registers

- Count of corrections

- 4. Measure SEU-induced bit error rate in data

- Tests the serializer/deserialzer + SRAMs

- Errors in deserializer and SRAM only visible in triggered-data

- Serializer errors appear in IDLES

Total Fluence: 4.99E13 protons/cm2

A bit limited - low L1A rate (3 Hz)

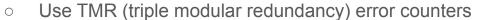

#### SEE Testing Setup

- Test two ECON-D-P1

- Neither are FIB'd chip

- Beam details

- Aperture 2 cm x 2 cm

- Continuous

- 217 MeV

- Flux varied per run (at request)

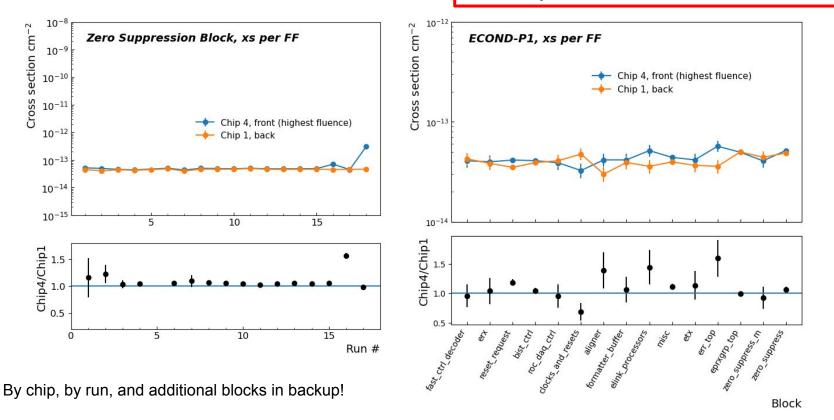

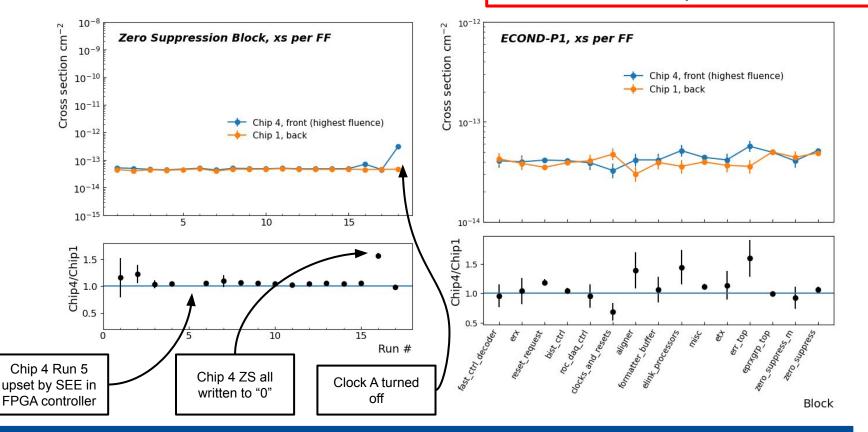

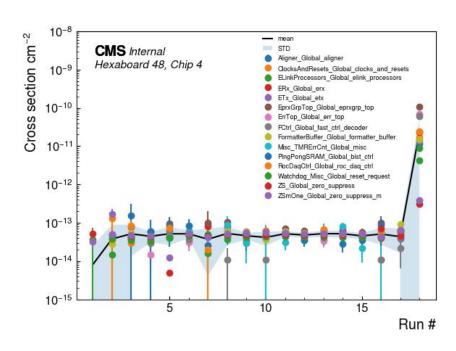

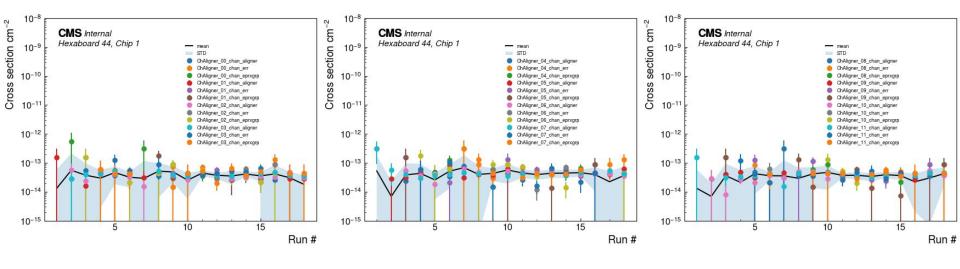

### Looking at Chip Comparisons

Cross section from counter of single bit flips that were then corrected!

### Looking at Chip Comparisons

Differences in chips due to fluence, as expected!

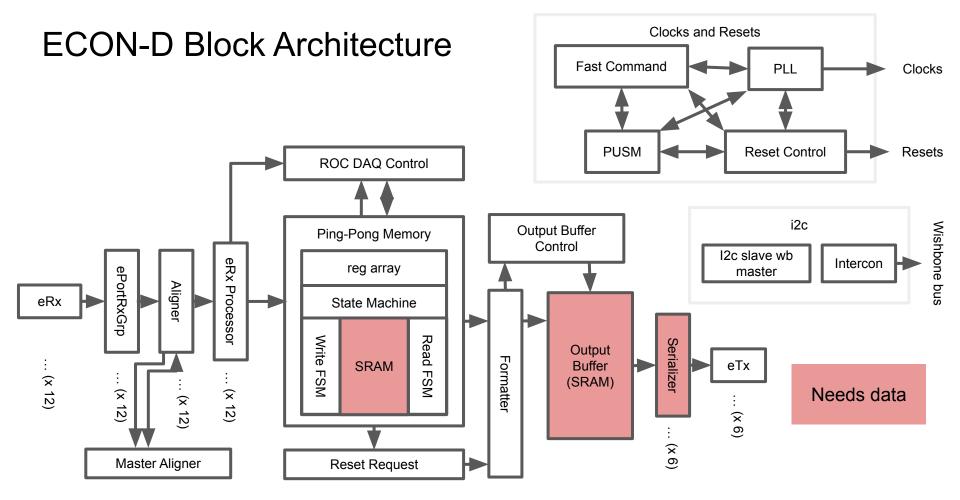

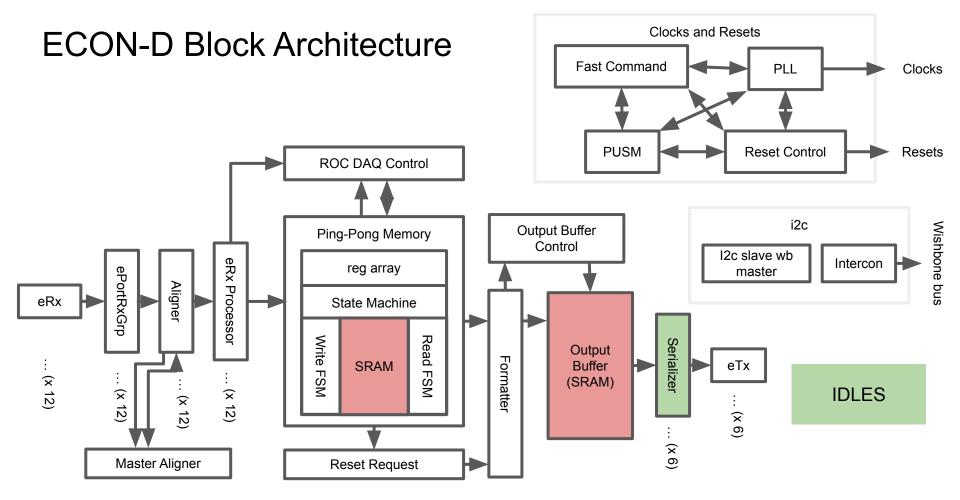

#### Bit error rate (BER) in eTx data

- Data errors taken from comparison of FPGA emulator and ASIC output

- BER observed in IDLE words ~ 4 x 10<sup>-10</sup> errors/word

- Tests serializer alone

- No bit errors observed in event packets → Cannot quote BER per trigger

- Trigger rate limited to 3 Hz for technical reasons\*\*

- Would test core logic + SRAMs + serializer

- Use SRAM dwell time to compute cross section limit:  $\sigma_{SRAM} < 1.1 \times 10^{-12} \text{ cm}^2/\text{bit}$

- assume SEUs arise in SRAM

- Upper limit on BER in "payload length" field of event packet BER<sub>payload</sub> < 0.5 Hz for 27k</li>

ECON-D on entire HGCAL.

- Computed using  $\sigma_{SRAM}$  and expected 750 kHz HL-LHC trigger rate

- "Payload length" protected by Hamming code for error correction in BE, if necessary

<sup>\*\*</sup>Low rate due to powering of chip-on-board → higher rates caused system instabilities that can be fixed with extra capacitance on the boards (discovered later)

#### SEE Testing Summary

- NO errors requiring reset observed

- Upper Limit on XS on SEE requiring reset 3x10<sup>-14</sup> cm<sup>2</sup>/ECOND

- ~ 13 mins without reset

- Smooth and successful

- Cross section for SEUs + Limits on errors requiring resets consistent with ECON-T-P1

- Cross section consistent across all measurements

- Across runs

- Chips

- Blocks

- Infrequent L1As were a limitation in the results, but we are confident in the performance, and plan more testing

Done at the CERN EP-ESE ObeliX facility

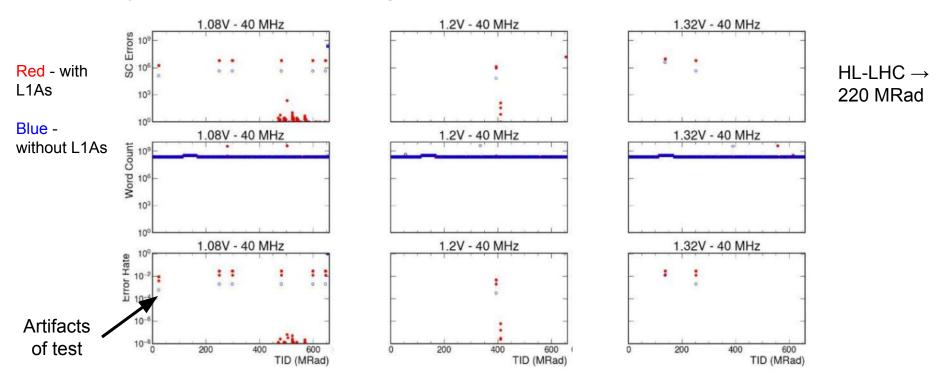

## **Total Ionizing Dose Testing**

#### Goals of Total Ionizing Dose (TID) Test

- 1. Characterize changes in behavior with dose

- PLL locking range and value

- Automatic cap-bank setting

- SRAMs

- Data quality

- 2. Test operation at different operating voltages w/ dose

- 3. Test operation at -30° C w/ dose

- 4. Ensure ECOND will continue to function as expected at the end-of-life dose

- And at a factor of 3 over the expected HL-LHC dose

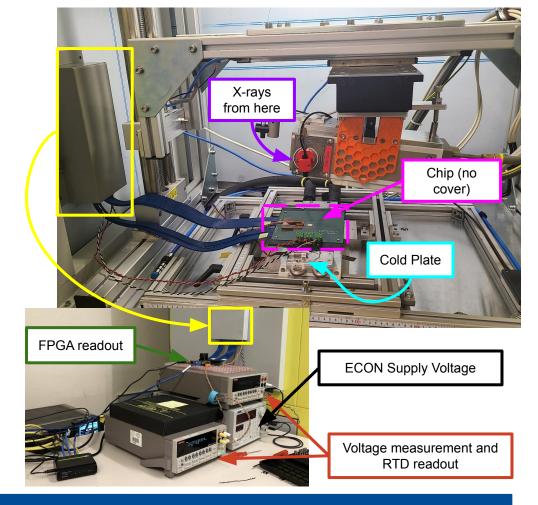

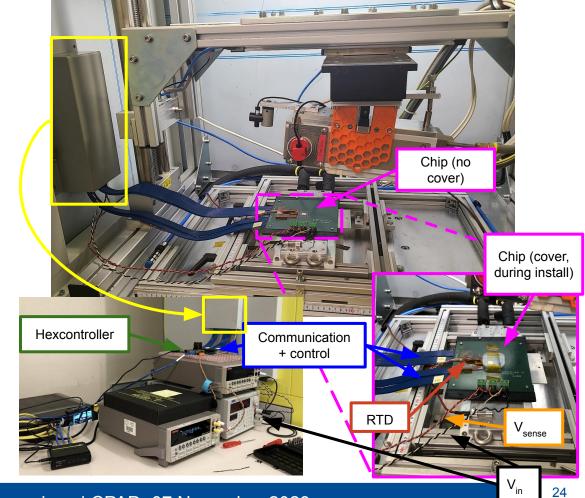

#### **TID Testing Setup**

- 3 Chips tested

- Cycled through supply voltages

- 1.2 V ± 10%

- 660 MRad desired dose

- ~9.2 MRad/Hour

- 72 hours per chip

- 3x safety margin

- X-rays

- Peak energy, 10 keV

- Cold plate held at -35°C

- Dry gas continuously flowing

### **TID Testing Setup**

- 3 Chips tested

- Cycled through supply voltages

- o 1.2 V ± 10%

- 660 MRad desired dose

- ~9.2 MRad/Hour

- 72 hours per chip

- 3x safety margin

- X-rays

- Peak energy, 10 keV

- Cold plate held at -35°C

- Dry gas continuously flowing

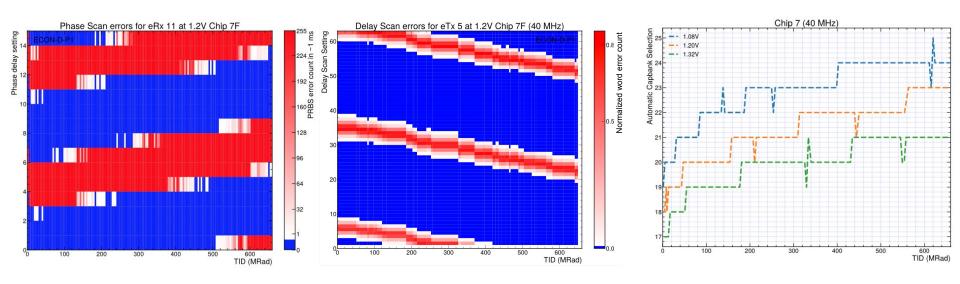

#### TID Testing Results - Phase, Delay, and Capbank Tests

Phase, delay, and capbank settings change with dose (as expected)

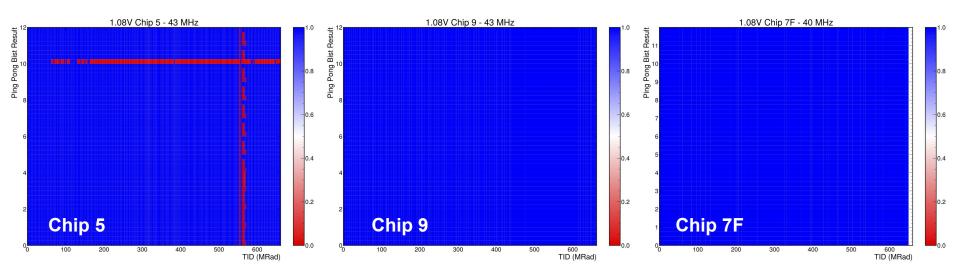

#### SRAM Tests - Ping pong

- At all nominal operation schemes (V<sub>in</sub> > 1.1), no errors

- Writing/reading SRAM address in Ping pong failed in one chip at 1.08 V

- Reproducible in most chips w/out dose at voltages < 1 V</li>

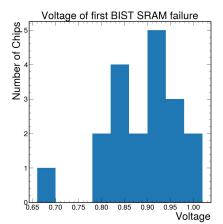

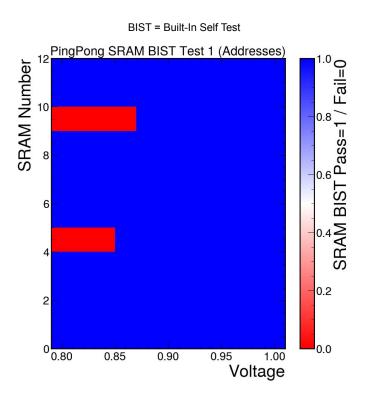

#### SRAM Tests - Ping pong → Bench

- At all nominal operation schemes (V<sub>in</sub> > 1.1

V), no errors

- Reproducible on bench at V<sub>in</sub> < 1 V</li>

- Effected SRAM varies

- Always happens in "test 1" → writing the SRAM address to the SRAM

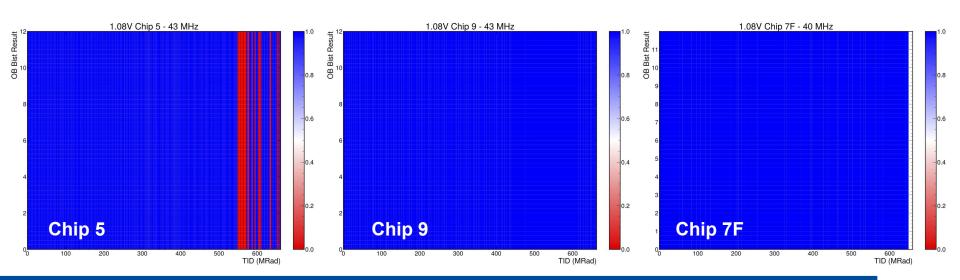

#### SRAM Tests - Output buffer

- At all nominal operation schemes (V<sub>in</sub> > 1.1), no errors

- Chip 5 failed once we could no longer achieve lock this is expected

- Can also see all 4 test failures in one SRAM at V<sub>in</sub> < 1 on bench</li>

- Curious, but way out of specifications

#### Stream Compare Errors

Only saw errors at low voltage in Chip 7F - 1.08 V and > 450 MRad

#### **TID Testing Summary**

- Expected behavior observed

- Gradual changes with settings and PLL width

- on par with ECON-T and IpGBT

- Operation OK at temperature and most voltages

- 1.08 V a bit spotty above 450 Mrad for data errors

- Ping pong issue in one out of the three chips at low voltage and dose

- Though this can be triggered at very low voltage on bench

### ECON-D-P1 Radiation Testing Summary

- All appears well!

- All measurements align with expectations

- SEE Testing

- SEE cross section tracks with ECON-T

- Limit on errors requiring reset  $\rightarrow$  3 x 10<sup>-14</sup> cm<sup>2</sup>/ECON-D

- ~ reset every 13 mins/per ECON-D

- Potential limitation on data errors due to low L1A rate

- TID Testing

- PLL and capbank behavior goes as expected

- Discovered limitation of SRAM at low voltage but all actual operation will be unaffected

Production versions of Production versions of ECON-D arrive ECON-T and ECON-D arrive will undergo ECON-T early next year! undergo ECON-T early chips will undergo the early chips will rest the early chips will be a production similar tests.

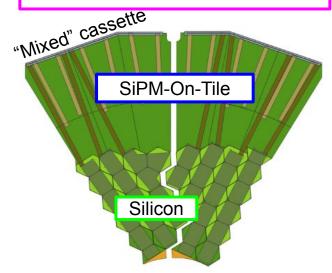

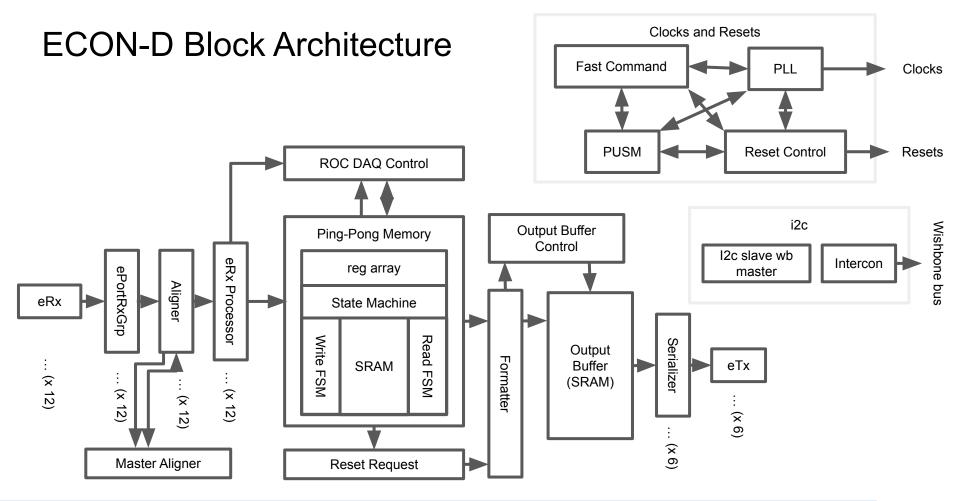

## back-up

#### HGCAL front end data path **ECON-T** Raw Data: Hexaboard with 6M Channels → 5 Pb/s, ~1M links\* **HGCROC** "Mixed" cassette readout ASICs **ECON-D** SiPM-On-Tile Concentrator Mezzanine IpGBT (TX) Silicon VTRx+ IpGBT (TX) Cu/W absorber plate kapton Silicon IpGBT (RX/TX) HGROC: 1M Channels → Sensor 300 Tb/s, 60k links\* Engine \*Assumes 40 MHz rate and 50% link packing efficiency for 10.24 Gbps \*\*Assumes 750 kHz rate (trigger) and 50% link packing efficiency for 10.24 Gbps

#### Tests completed

| Run | Time [s] | Flux [p/cm2/s] | Fluence [p/cm2] | Tot Fluence [p/cm2] |

|-----|----------|----------------|-----------------|---------------------|

| 1   | 52       | 2.55E+08       | 1.32E+10        | 1.32E+10            |

| 2   | 100      | 7.50E+08       | 7.50E+10        | 8.83E+10            |

| 3   | 159      | 1.68E+09       | 2.66E+11        | 3.55E+11            |

| 4   | 158      | 4.41E+09       | 6.96E+11        | 1.05E+12            |

| 5   | 117      | 8.60E+09       | 1.01E+12        | 2.06E+12            |

| 6   | 126      | 1.60E+10       | 2.01E+12        | 4.07E+12            |

| 7   | 30       | 4.58E+09       | 1.37E+11        | 4.20E+12            |

| 8   | 56       | 1.70E+10       | 9.50E+11        | 5.15E+12            |

| 9   | 180      | 1.59E+10       | 2.87E+12        | 8.02E+12            |

| 10  | 60       | 1.60E+10       | 9.60E+11        | 8.98E+12            |

| 11  | 609      | 1.58E+10       | 9.63E+12        | 1.86E+13            |

| 12  | 635      | 1.65E+10       | 1.05E+13        | 2.91E+13            |

| 13  | 194      | 1.63E+10       | 3.16E+12        | 3.22E+13            |

| 14  | 543      | 1.65E+10       | 8.94E+12        | 4.12E+13            |

| 15  | 354      | 1.64E+10       | 5.81E+12        | 4.70E+13            |

| 16  | 59       | 1.64E+10       | 9.66E+11        | 4.79E+13            |

| 17  | 58       | 1.64E+10       | 9.53E+11        | 4.89E+13            |

| 18  | 59       | 1.63E+10       | 9.65E+11        | 4.99E+13            |

|     |          |                |                 |                     |

Total Fluence: 4.99E13 protons/cm2

#### 3 special tests:

Run 16 → ZS written to all 0, ZSm1 written to all 1 (Chip 4) Run 17 → ZS written to all 1, ZSm1 written to all 0 (Chip 4) Run 18 → Clock A turned off (Chip 4)

Difference in rate of SEU in 0 and 1's

Test triplication

#### Looking at SEU xs - All blocks but Channel Aligner

#### Consistent across runs and blocks

#### Looking at SEU xs - All ChAligner blocks - Chip1

#### Bit error rate in eTx data - Dwell Time

- 3 L1As 1000 BX apart each second

- Low rate due to powering of chip-on-board → higher rates caused system instabilities that can be fixed with extra capacitance on the boards (discover later, Danny's talk)

- No errors observed in packets

- Have to use dwell time weighted bits to get an upper limit on SEU cross section in SRAMs

$$N_{\rm bits} \cdot t_{\rm dwell} \cdot \phi_{\rm test} = (780k \ {\rm bits} \cdot {\rm BX/evt}) \cdot (2933 \ {\rm s}) \cdot (3 \ {\rm evts/s}) \cdot (1.63 \times 10^{10} \ {\rm cm^{-2} \ s^{-1}})$$

=  $2.8 \times 10^{12} \ {\rm cm^{-2} \ bits}$

- 1.1 x 10<sup>-12</sup> cm<sup>2</sup>/bit upper limit on cross section of errors in SRAMs

- Upper limit on errors in packet length for the entire detector at event rate of 750 kHz is 0.5 Hz

- Protected by Hamming code

- "Error" → comparison between ASIC and emulator