#### <u>CPAD 2023 - November 7th 2023</u>

Design and characterization of sub-10ps TDC ASIC in 28nm CMOS technology for future 4D trackers

Larry Ruckman - ruckman@slac.stanford.edu

Valentina Cairo, Angelo Dragone, Aseem Gupta, Bojan Markovic, Julian Mendez, Aldo Pena Perez, Lorenzo Rota, Ariel G. Schwartzman, Dong Su, Caterina Vernieri

## Motivation

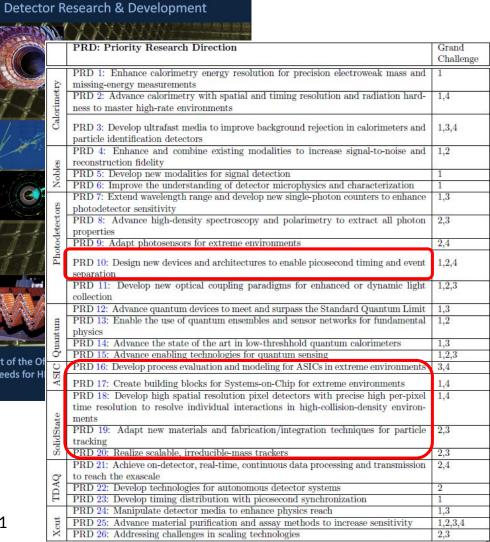

# **2019 DOE Basic Research Needs Study on High Energy Physics Detector Research and Development**

- Future high energy, high luminosity hadron colliders will present much higher levels of pileup and extreme radiation environments

- Future detectors will require higher segmentation (3D position resolution) and additional time resolving capabilities while sustaining higher radiation doses (Instrumentation BRN Science Driver: Higgs and the energy frontier PRD10, PRD16, PRD17, PRD18, PRD19, PRD20)\*

- To satisfy requirements front-end sensors and readout ASICs will need to be compatible with:

- Larger channel density Low power, Smaller feature size (Deep sub-micron technologies)

- Unprecedented radiation levels (dose of up to 30 GRad and 10<sup>18</sup> neutrons/cm<sup>2</sup>)

- Precision timing resolution fast sensors, in pixel high precision timing circuits

28nm CMOS

TDC design

\*Similar Detector Research and Development Themes (DRDTs) are identified in the 2021 European Committee for Future Accelerators (ECFA) Detector R&D (DRD) Roadmap

Basic Research Needs for High Energy Physics

## 28nm TDC Architecture

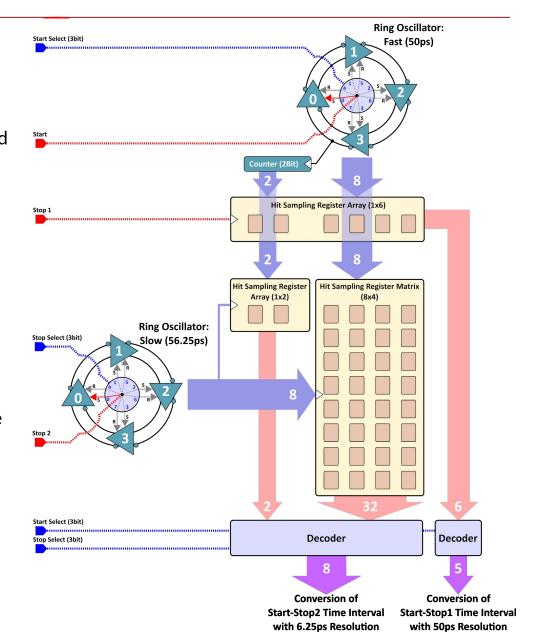

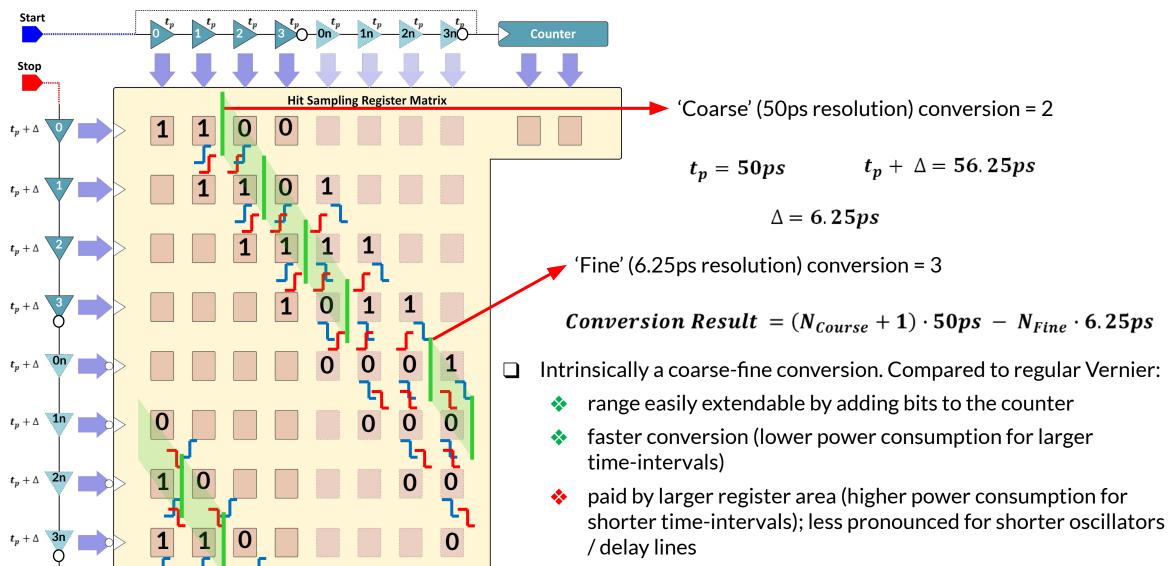

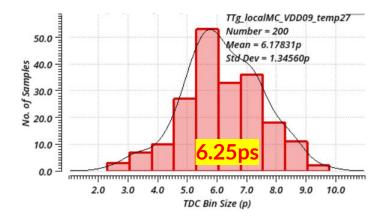

#### 2D Vernier Architecture:

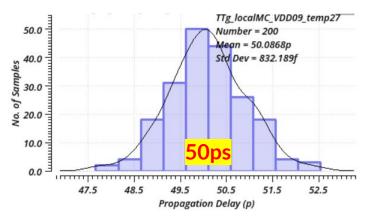

- Fast Ring Oscillator with 50ps propagation delay cells;

- Slow Ring Oscillator with 56.25ps propagation delay cells;

- START + two STOP signal for simultaneous Time-Of-Arrival (TOA) and Time-Over-Threshold (TOT) measurements;

- Start-Stop1 Coarse time resolution (TOT): 50ps;

- Start-Stop2 Fine time resolution (TOA): 56.25ps 50ps = 6.25ps;

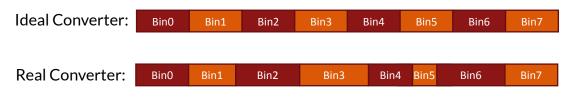

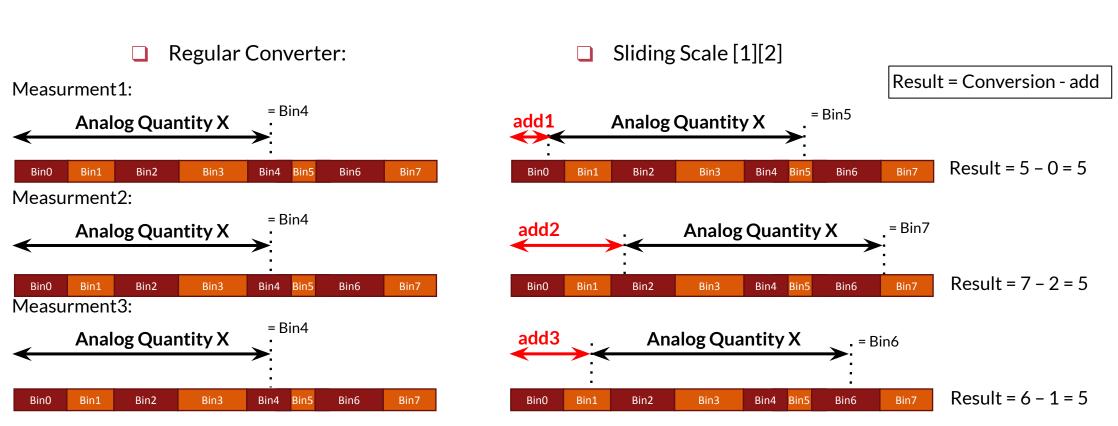

- Sliding scale technique for improvement of conversion linearity:

- Both ring oscillators have programable starting conditions via delay cell set/reset function;

- Starting conditions randomly selected each measurement cycle and corresponding values subtracted from the conversion result;

- Same time intervals converted with different parts/bins of the TDC conversion characteristics;

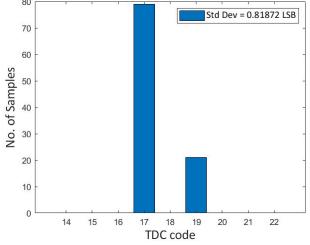

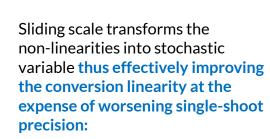

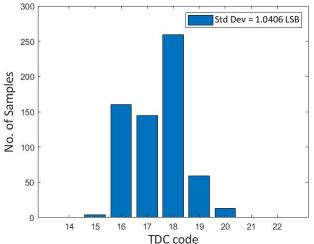

- Sliding scale transforms the non-linearities into stochastic variable thus effectively improving the conversion linearity at the expense of worsening single-shoot precision.

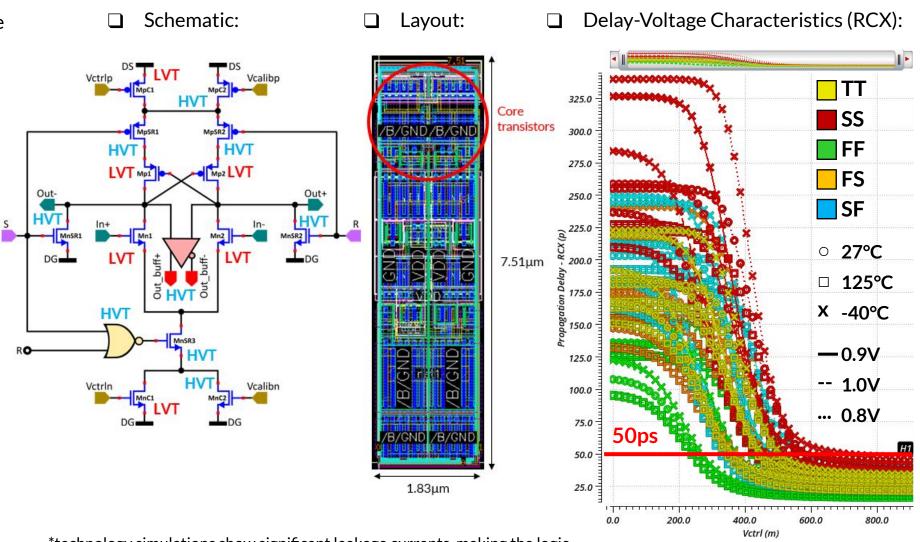

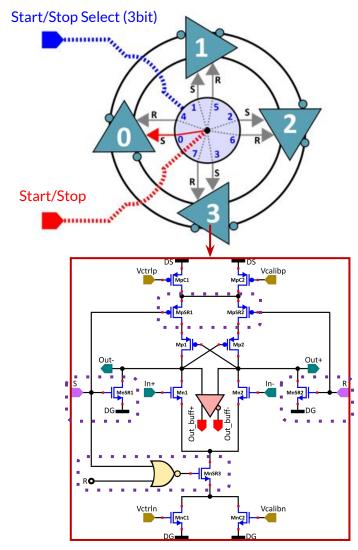

# Voltage-Controlled Delay Cell (VCDC)

- Differential Cascode Voltage Switch Logic (DCVSL) implementation

- Current-starved approach for propagation delay control

- Calibration / Trimming

- Output buffer for driving thε state-sampling registers

- Set/Reset logic controls

- Leakage reduction\*:

- Non-minimum length (35nm) used for all transistors

- Low Voltage Threshold (LVT) used for speed-critical transistors

- High Voltage Threshold (HVT) transistors in series between supply and ground

\*technology simulations show significant leakage currents, making the logic static power consumption not negligible (especially at higher temperatures)

# 2D Vernier TDC - Operation

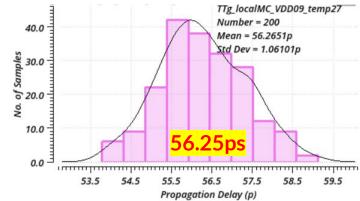

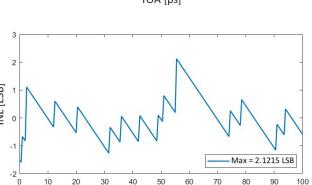

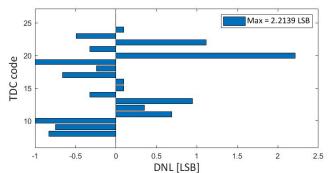

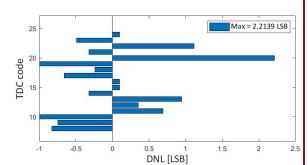

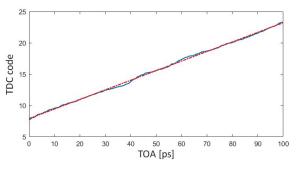

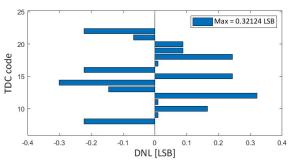

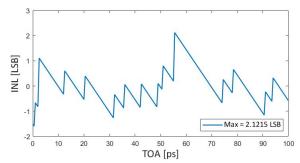

# 2D Vernier TDC - Mismatch (sliding scale disabled)

☐ Delay Cell Mismatch (RCX, Global Corner + Local MC, N° of runs: 200):

2D Vernier TDC characteristics with mismatch (Global Corner + Local MC, one iteration):

TOA [ps]

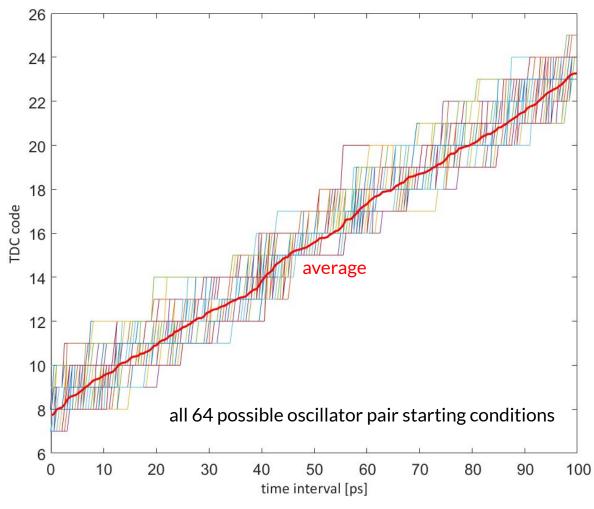

# Sliding-Scale Implementation

#### Sliding-Scale technique [1,2]:

- Both ring oscillators have programable starting conditions via delay cell set/reset function;

- Starting conditions randomly selected each measurement cycle and corresponding values subtracted from the conversion result;

- Same time intervals converted with different parts/bins of the TDC conversion characteristics;

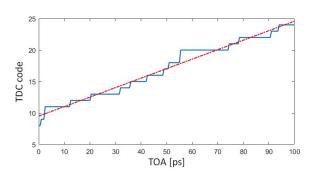

#### ☐ TDC characteristics with mismatch:

[1] C. Cottini, E. Gatti, and V. Svelto, "A new method for analog to digital conversion," Nucl. Instr. Meth., vol. 24, p. 241, Aug. 1963.

[2] E. Gatti, P. F. Manfredi, and D. Marino, "Analysis and characterization of cyclic-scale compensated analog-to-digital converters," Nucl. Instrum. Methods, vol. 165, no. 2, pp. 225–230, Oct. 1979.

# 28nm TDC Architecture - Sliding Scale

#### ☐ TDC characteristics with sliding scale disabled

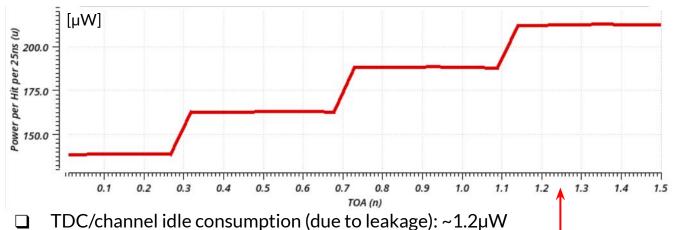

## 28nm TDC - Power, Conversion Time, Area

Average power within 25ns window VS TOA (RCX):

- TDC/channel power consumption depends on time-interval being measured

- For uniformly distributed time-intervals *Ti* the average power consumption per Hit in a 25ns measurement window is:

$$P_{\frac{av}{hit}/T_{CK}} = 173 \mu W$$

**Average** power consumption:

$$P_{av} = 1.2\mu W \cdot (1 - Occupancy) + P_{\frac{av}{hit}/T_{CK}} \cdot Occupancy$$

- For 10% occupancy: ~ 18.4µW

- For 1% occupancy: ~2.9µW

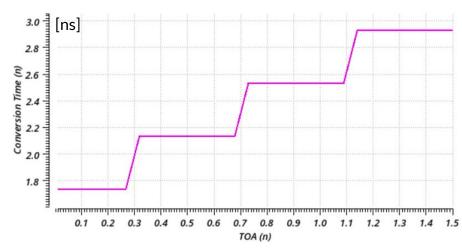

Time between Start signal and the end of conversion VS TOA (RCX):

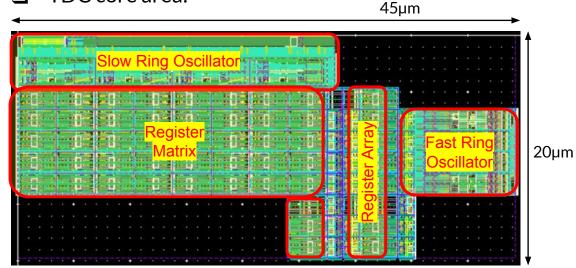

TDC core area:

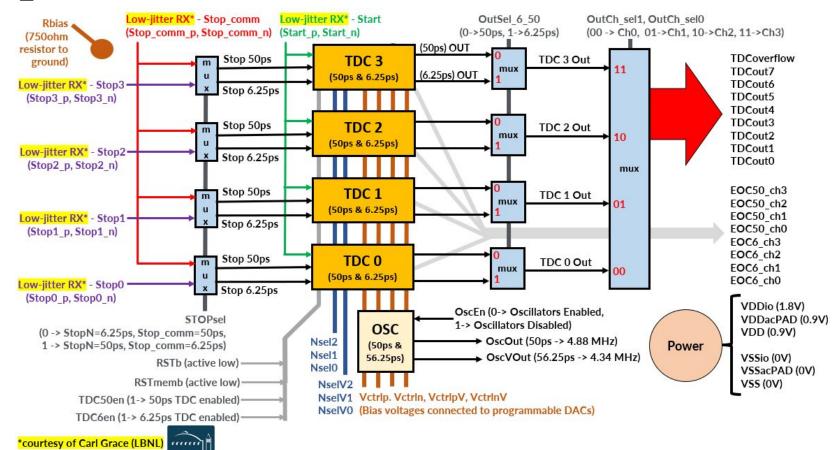

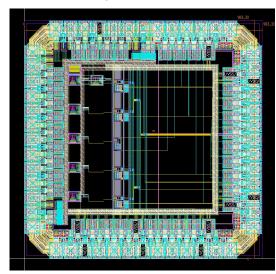

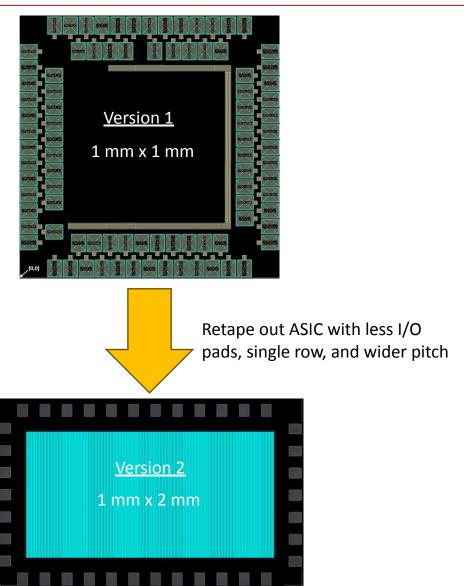

# 28nm TDC ASIC prototype

#### ☐ ASIC block schematic:

- 4 TDC channels, each with 50ps and 6.25ps sections

- Common Start, a common Stop1 and 4 separated Stop2 inputs

- Low-jitter receivers provided by LBNL

- Fast and Slow Oscillators for propagation delay control

#### **ASIC** layout:

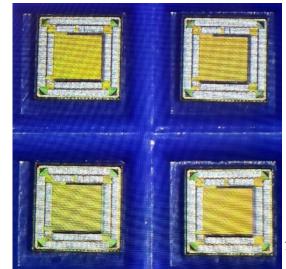

#### ☐ ASICs photo:

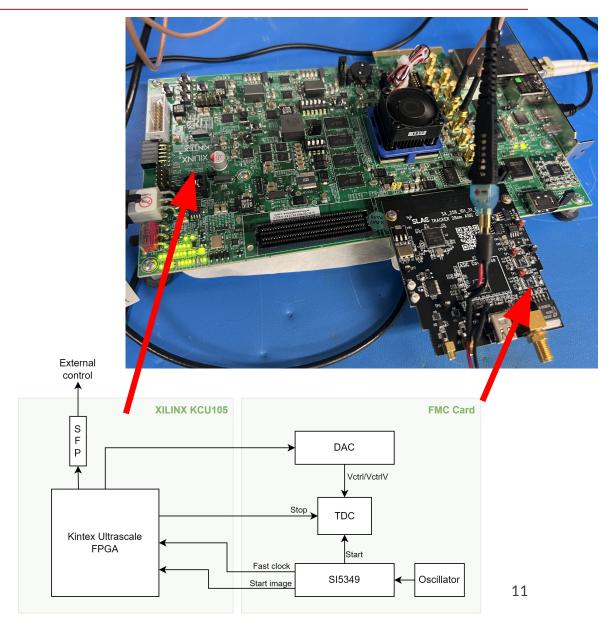

# Development Board and custom ASIC Carrier

- AMD/Xilinx KCU105 development board for FPGA (KU040)

- FMC card for the ASIC carrier

- Power regulation

- Level translation

- Low jitter PLL reference

- Connectors for external reference and inputs option

- PLL (SI5349) provides start and stop signal sources:

- Start signals directly comes from a PLL output

- Jitter measurement: 2.6 ps-RMS

- Output start images to the FPGA constant phase

- Provide fast clock signal that is used to shift the start signal

- DAC allows testing the ring oscillator reply in frequency

- External control through 10 Gbps serial link

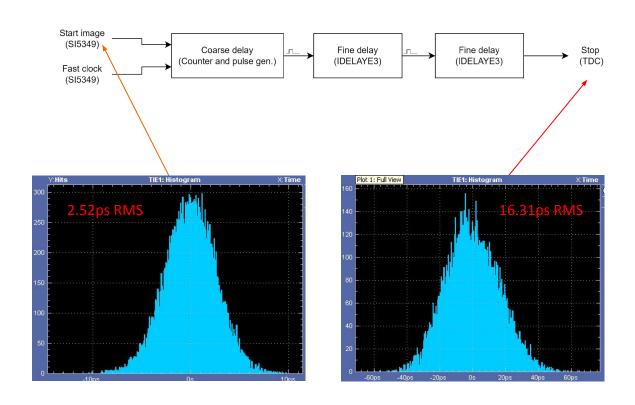

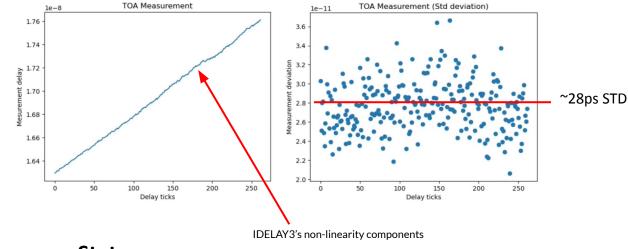

# FPGA Calibration pulse results and path forward

#### TOA measurements (calibration):

- Measured using high speed scope (Tektronix DPO7254)

- Averaged over 1000 samples

- Max. Std deviation of 35ps

#### Status:

- Good enough for the 50ps/step linear sweeping

- But <u>not</u> good enough for 6.5ps/step

- Can be used to qualify the 50ps configuration

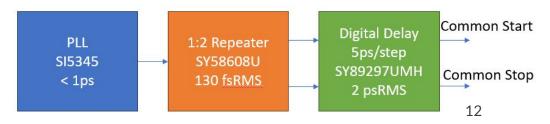

#### Path forward:

Use of external delay line (SY89297UMH)

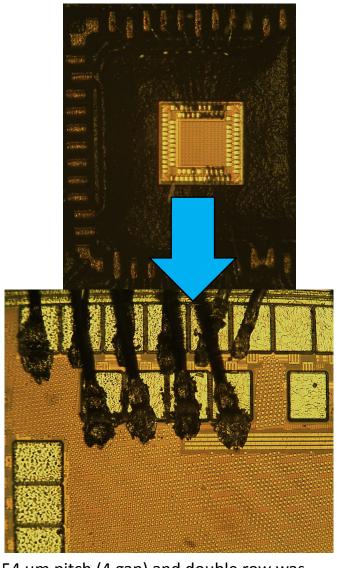

# ASIC + PCB Wire bonding Issues

$54 \ \mu m$  pitch (4 gap) and double row was too aggressive for the wire bonding pads

# Summary and Future Plans

## First tape out of 28nm at SLAC:

As with any new technology node, there are large learning curves to overcome

## Custom ASIC PCB carrier and FPGA firmware/software has been developed

- Calibration sweep circuit meets the 50ps/step requirement

- Expecting much lower jitter in the common stop (< 3p-RSM) in the next ASIC carrier revision with new delay IC circuit

## ASIC bonding pad placement was too aggressive in Version 1:

- Lesson learned: Getting feedback from wire bonding vendor and their recommendation prior to tape out

- Version 2 will use a less aggressive pad pitch (Early 2024 tape out)

# Backup

# Linearity Improvement: Sliding-Scale

[1] C. Cottini, **E. Gatti**, and V. Svelto, "A new method for analog to digital conversion," Nucl. Instr. Meth., vol. 24, p. 241, Aug. 1963.

[2] **E. Gatti**, P. F. Manfredi, and D. Marino, "Analysis and characterization of cyclic-scale compensated analog-to-digital converters," Nucl. Instrum. Methods, vol. 165, no. 2, pp. 225–230, Oct. 1979.

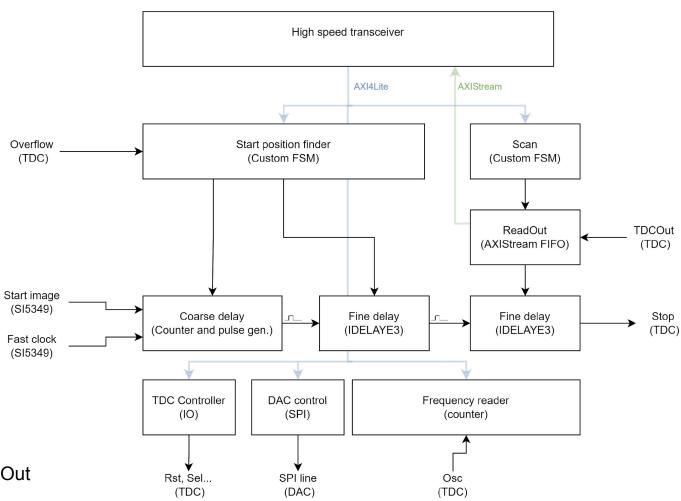

# Readout Block Diagram

#### Controlled via an AXI-Lite bus:

- Configure TDC via memory mapped registers

- Set DAC to configure the TDC's oscillators

- Read TDC's oscillator frequency

- Start and get status of custom FSMs

#### Start position finder:

- Search for the first non-overflow value

- Generate stop pulse sync with start

- Shift stop pulse by fast clock period steps

- Set the 0 position with 5ps accuracy (IDEALYE3)

#### Scan and readout:

- Set fine delay position (increment of 5ps)

- Generate AXI stream frame with position and TDCOut