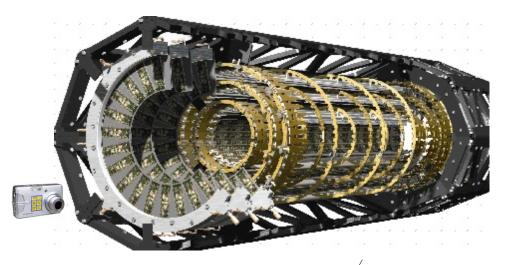

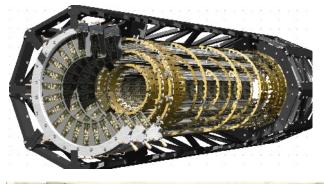

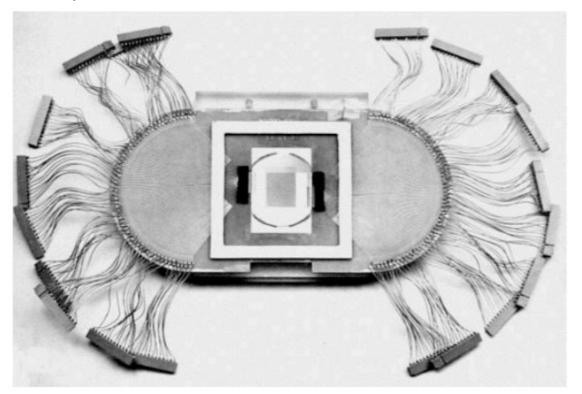

Close-up of ATLAS pixel detector, installed in 2007

#### June 19

# M/S Pledge

I pledge to not use the words Master and Slave to designate components or roles in circuits, systems,

https://sites.google.com/view/mspledge/

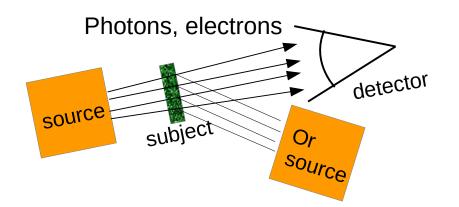

## **Imaging Particles**

High energy charged particles

- What you're used to:

- Detector to completely stops photons

- Lots of photons- every pixel gets some- source intensity limited on purpose

- Integrate or count many photons per channel

- Crucial differences for Imaging high energy charged particles

- Want particles to pass thorough imaging detector (aka tracker) as if it was not there. There are other detectors behind it

- There is no sample. We are looking at the quantum vacuum. Want intensity as high as possible.

- Measure every particle individually

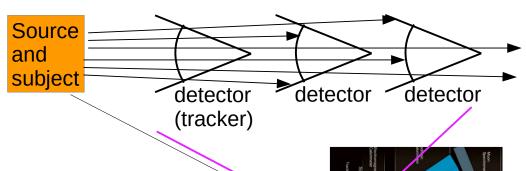

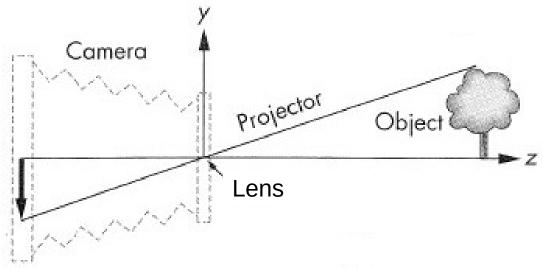

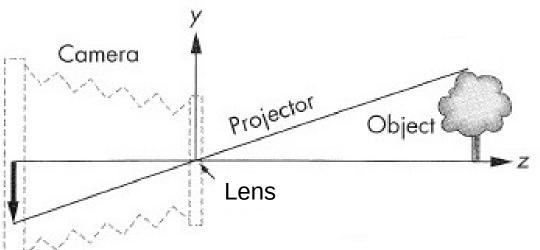

# Inverse problem to usual imaging

# Inverse problem to usual imaging

Particle trajectories

Clear?

## Let's do it

Let's build ourselves a silicon pixel tracking detector

#### Let's do it

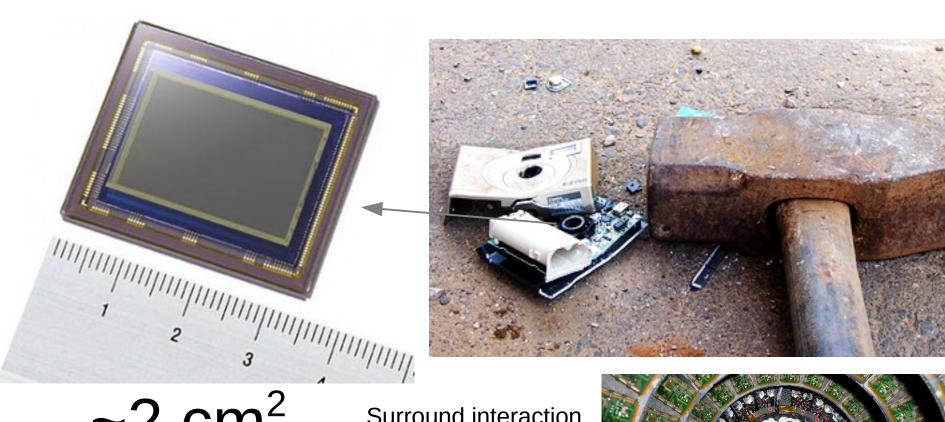

~2 cm<sup>2</sup>

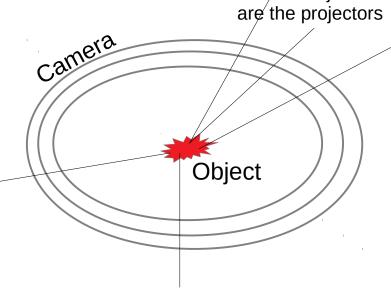

Surround interaction point with few layers of sensors

~100 000 cm<sup>2</sup>

(\$500K plus tax)

#### Will it work?

## Back to the drawing board

OK, so this thing can do 30 fps right?

• Then instead of 50,000 sensors we need (40,000,000 / 30) \* 50,000 = 65B sensors, which will only cost us \$650B. Maybe we can get a volume discount?

•

•

•

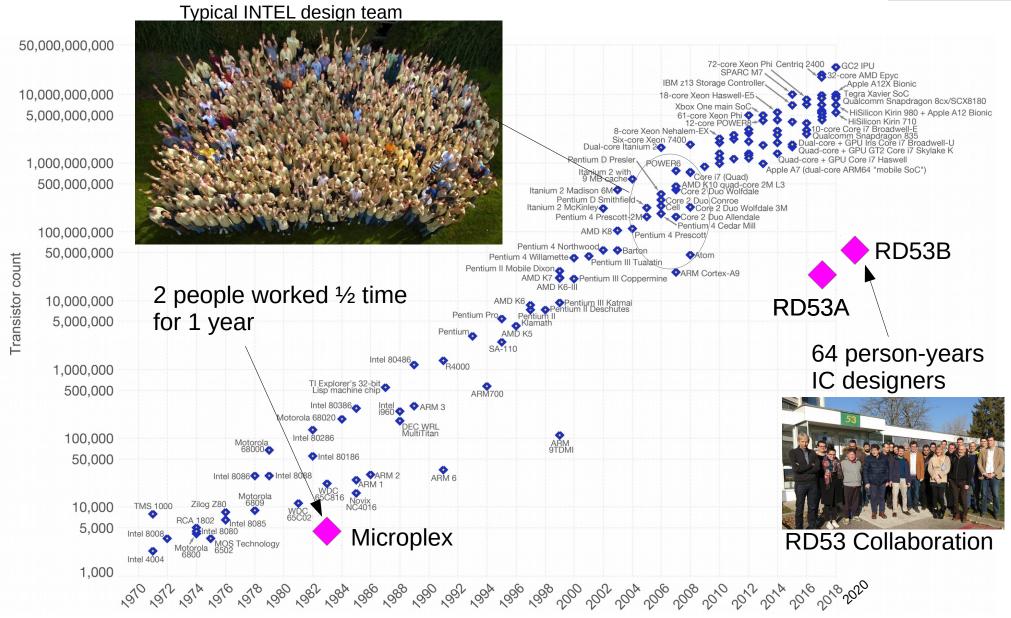

- And that's why we need custom ASICs to make tracking detectors

- Review how they're actually made next (or just remember the tour)

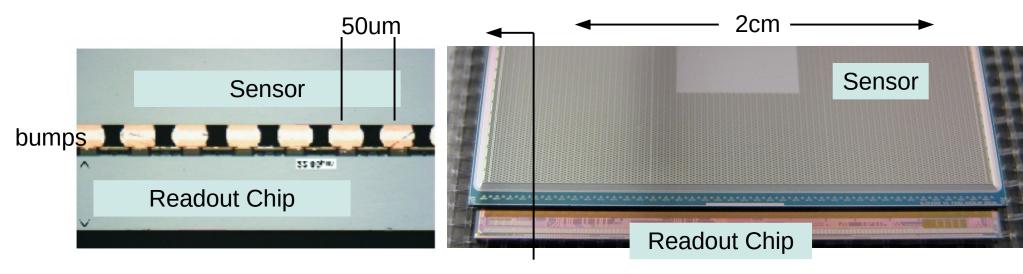

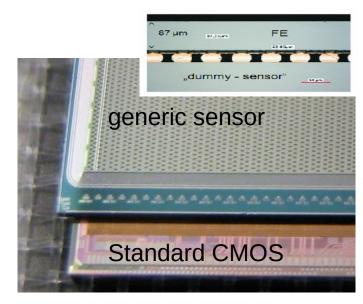

## Hybrid Pixel Detector Technology

ATLAS

PIXEL

2007

80M pixels

ATLAS

IBL

2014

12M pixels

ATLAS ITK 2026, 5G pixels

Remember the tour...

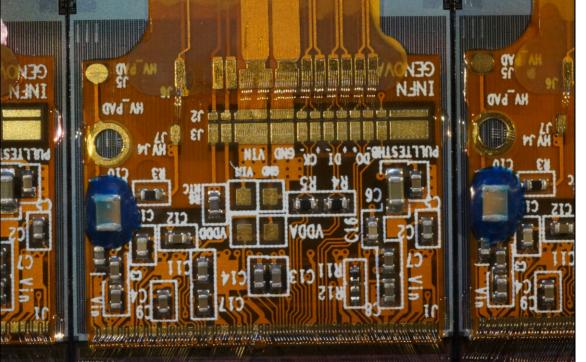

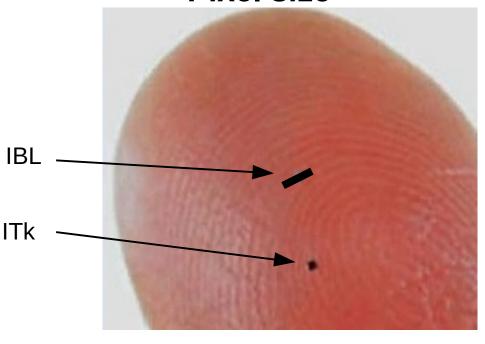

# Hybrid Pixel Technology (IBL)

#### ATLAS beam pipe layer (IBL)

Radiation dose: 5x10<sup>15</sup> n\_eq/cm<sup>2</sup>

"Frame rate": 40 MHz

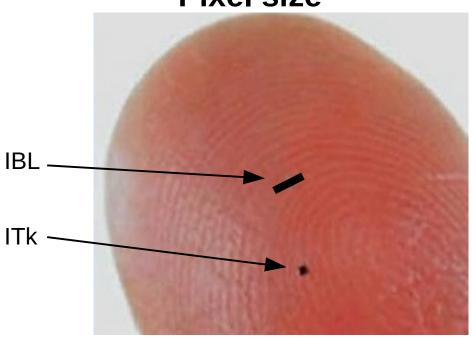

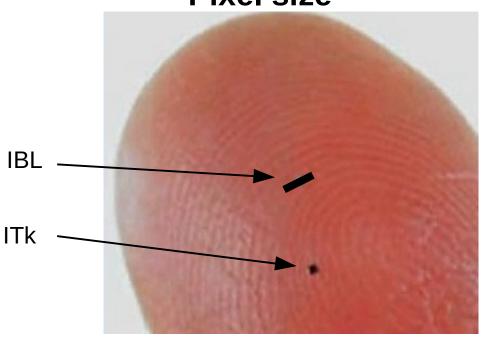

Pixel size: 50μm x 250μm

Silicon area: 0.15 m<sup>2</sup>

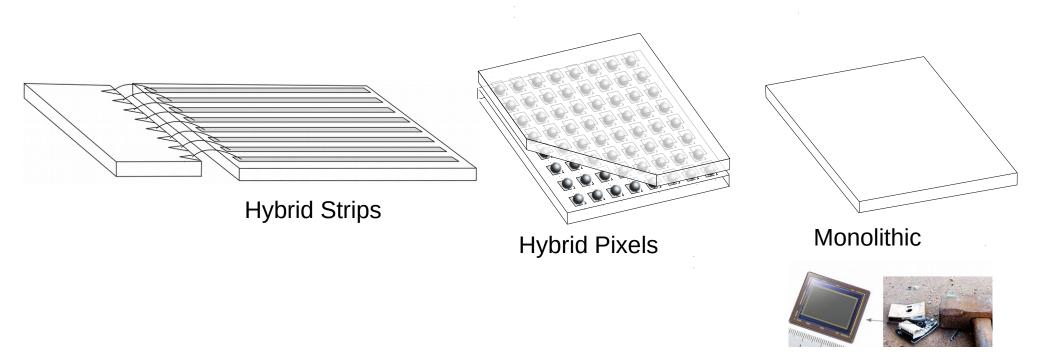

# Silicon Tracker Types

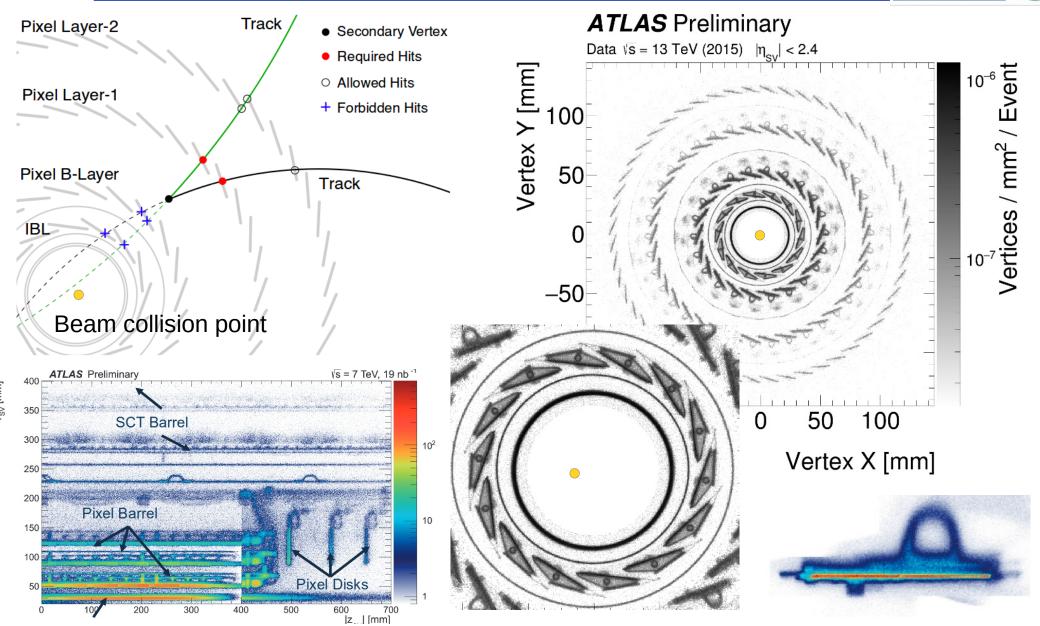

# Detector can image itself in 3D

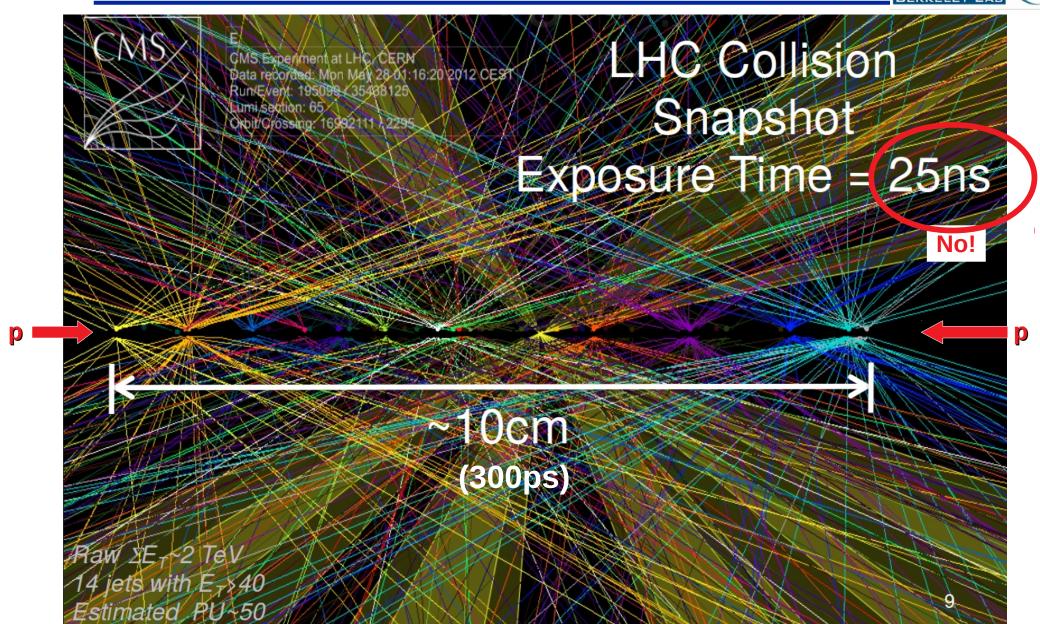

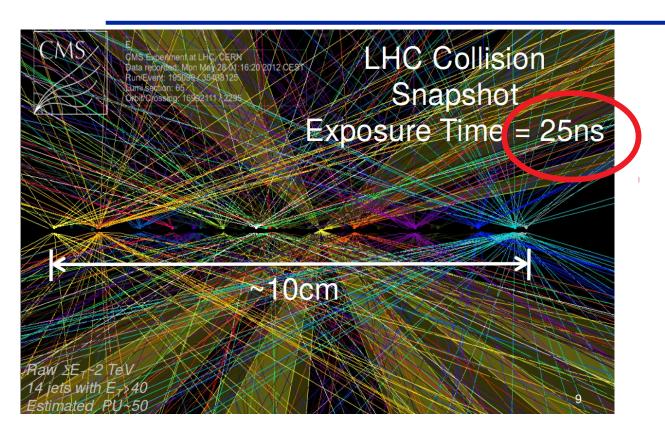

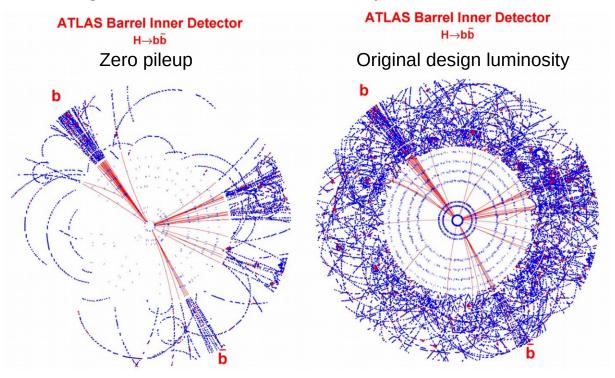

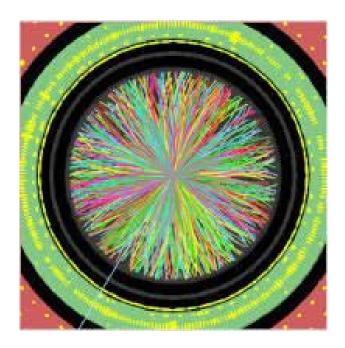

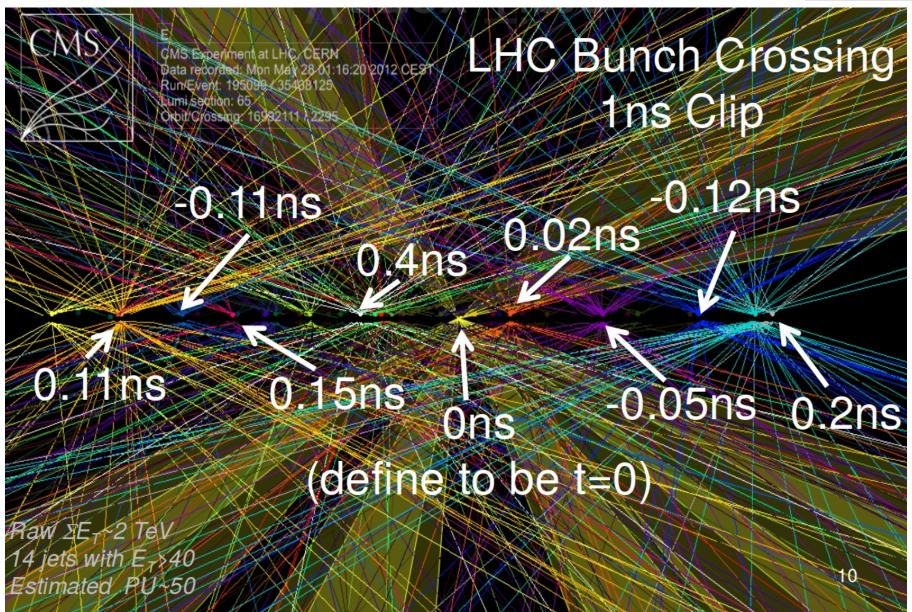

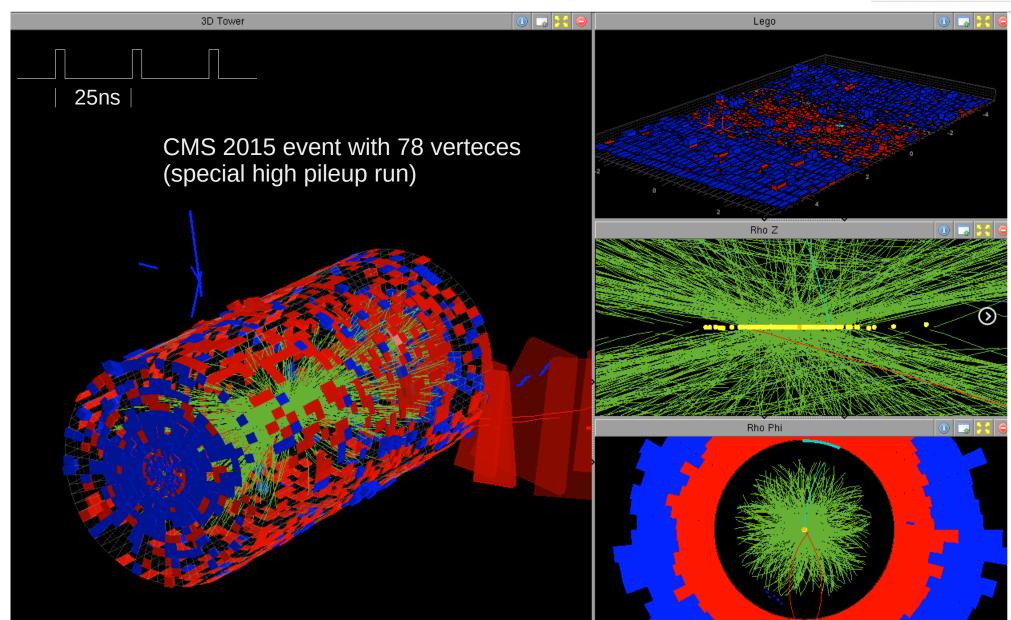

#### But how do we handle the rate?

- Capturing 40M 5Gpixel images per second is not feasible.

- Triggering only saves a factor of 40 in readout

- 1M 5Gpixel images per second is still far from feasible

- A: We do NOT do conventional image capture.

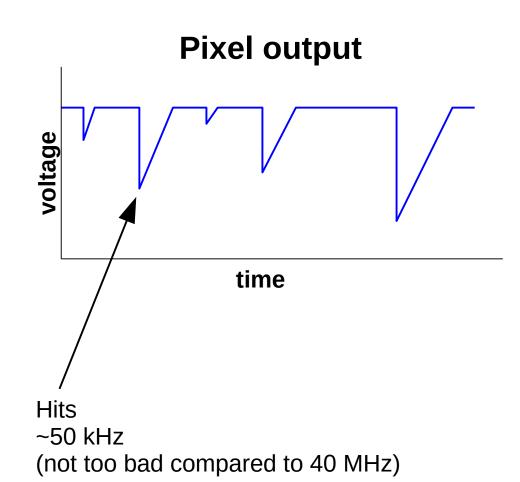

- We treat every pixel as an independent, free-running detector and store it's output (heavily redacted)

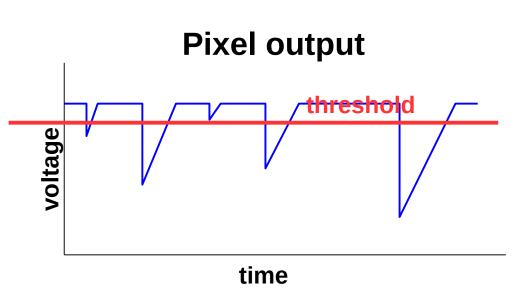

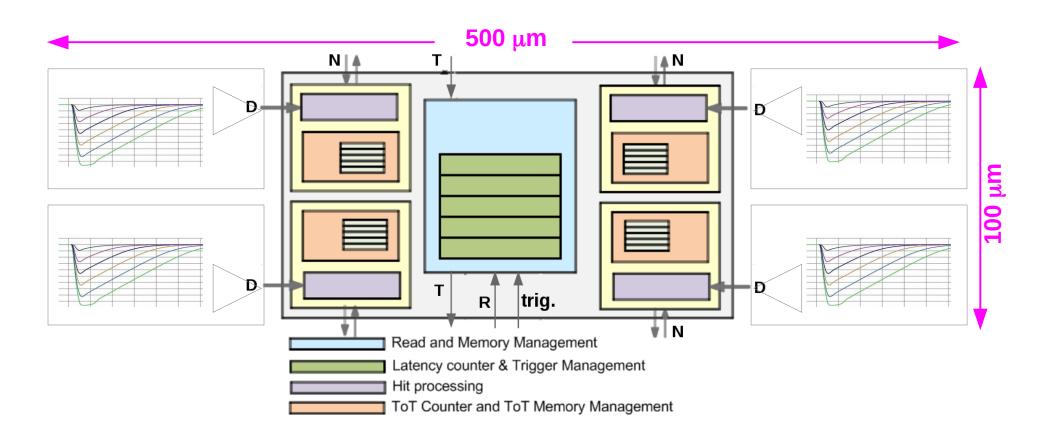

# Single Pixel Perspective

#### **Pixel size**

# Single Pixel Perspective

#### **Pixel size**

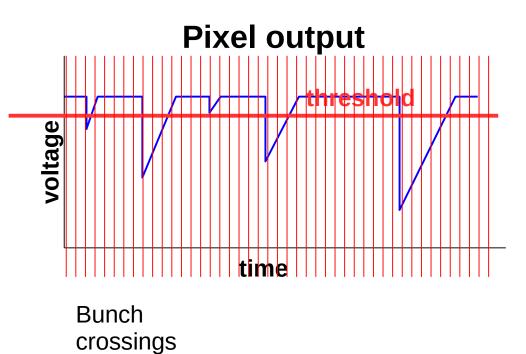

# Single Pixel Perspective

#### Pixel size

Digitize amplitude above threshold in each Bunch Crossing

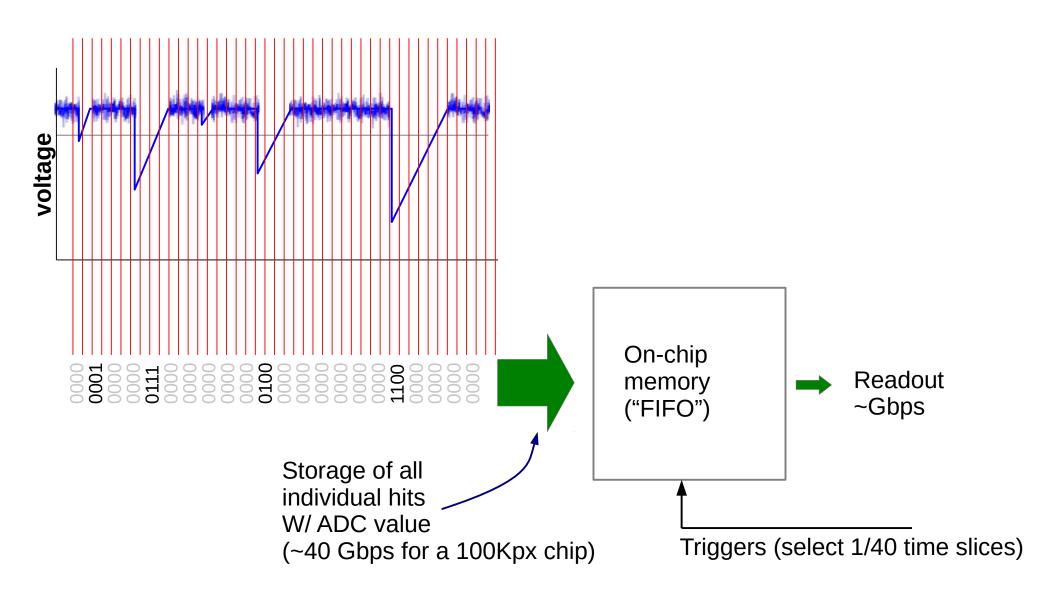

# On-Chip Storage and Trigger

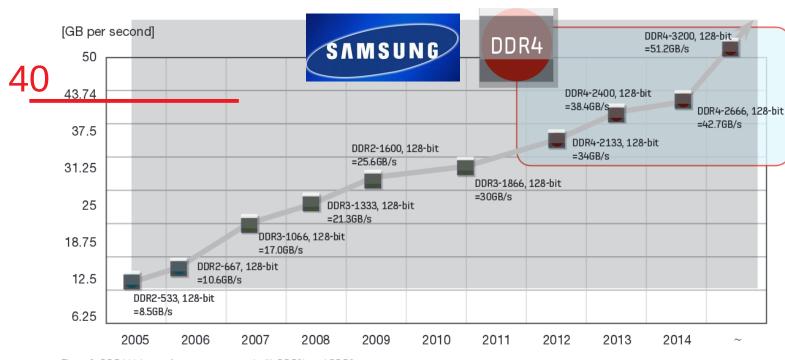

# **HEP** Did I just say a chip is storing 40Gbps?

High rate pixel readout chips are memories (in addition to being pixel readout chips)

Plot is for a memory module containing 8 silicon chips so B = b

Figure 2. DDR4 higher performance compared with DDR3L and DDR2

(and this is not rad hard)

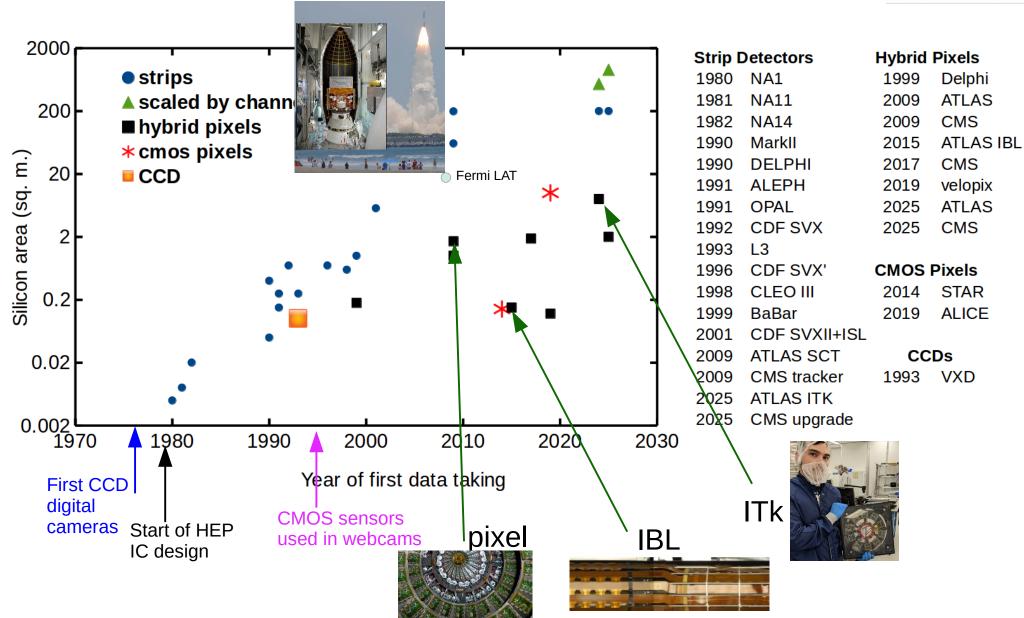

### Silicon Detectors at Colliders

BERKELEY LAB

(and in orbit)

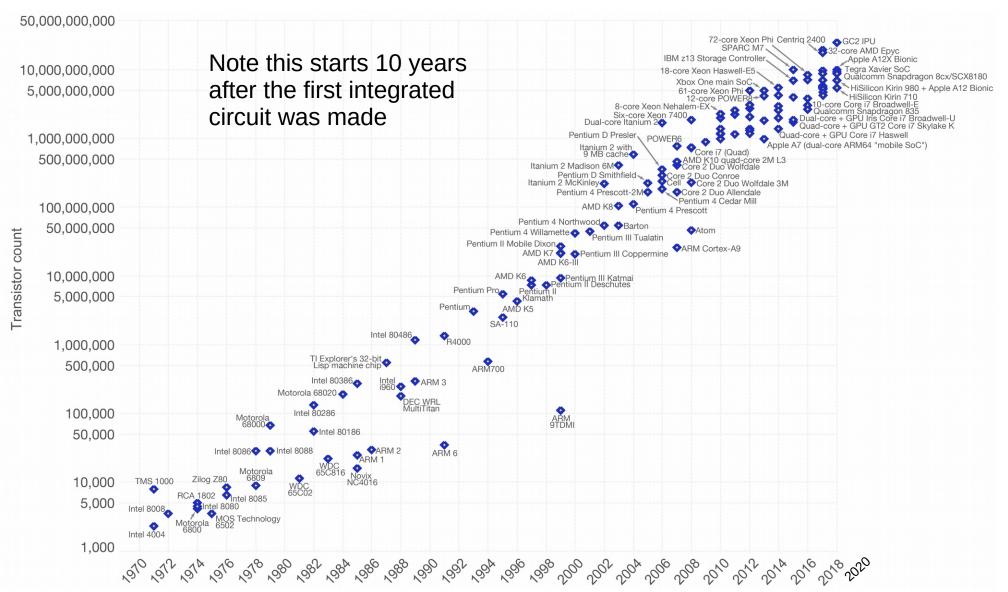

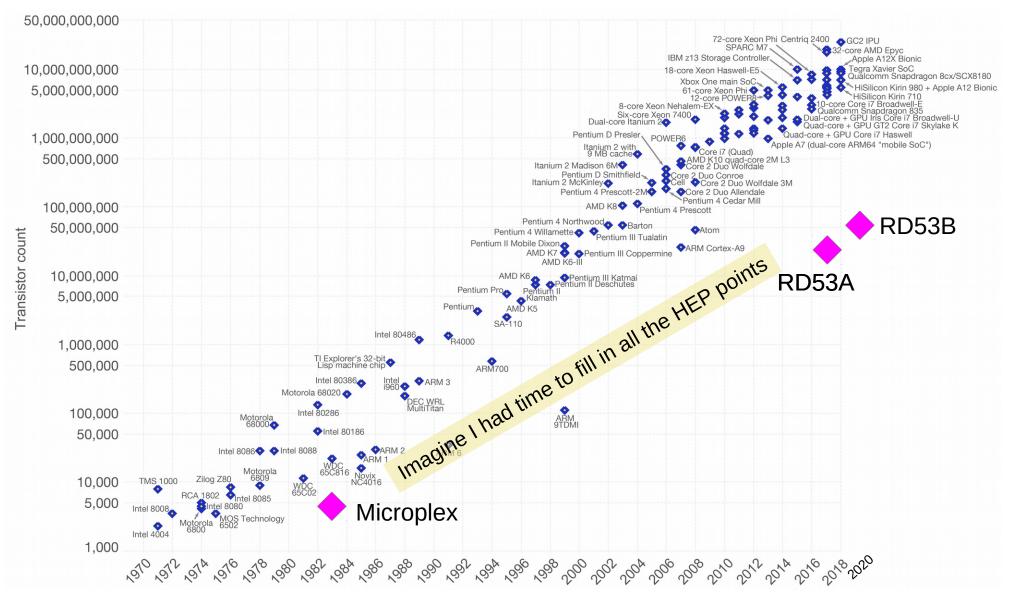

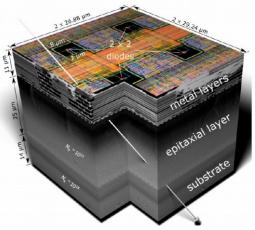

## Computer Processor

## **HEP Tracker Integrated Circuits**

# Why Microplex?

Because this was a silicon strip module before:

NA11, CERN 1981

NIM205 (1983) 99

It did not scale

## Why Microplex?

#### Original ATLAS motivation for pixels circa 1995

#### HL-LHC is far beyond

readout chip

Solution:

16 chips. 46,080 bump bonds

Xray of bumps

6.3cm

It did not scale.

A new readout chip solution had to be developed

#### Modern chip design needs large effort

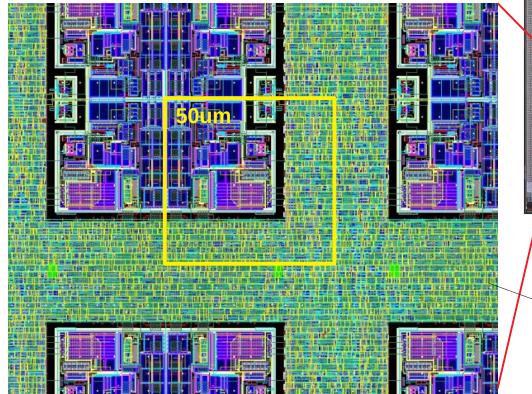

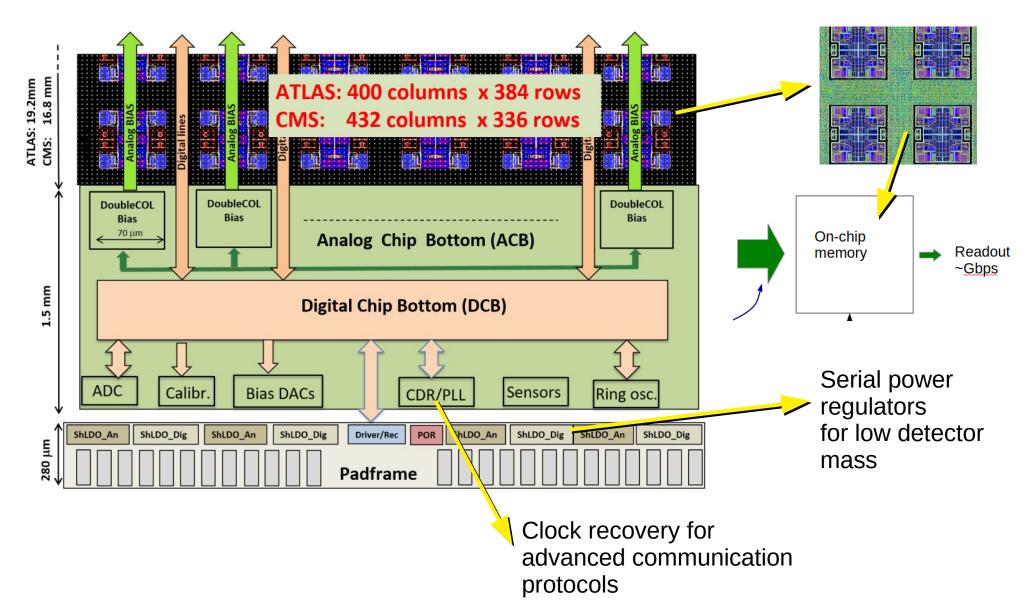

# RD53 Hybrid Pixel Readout 100x higher rate and radiation

Cern.ch/rd53

#### RD-53 Collaboration Home

RD-53 will design and produce the next generation of readout chips for the <u>ATLAS</u> and <u>CMS</u> pixel detector upgrades at the <u>HL-LHC</u>. More details can be found in the <u>2018 extension proposal</u> and the original <u>collaboration proposal</u>.

~1000 transistors

June. 20, 2023

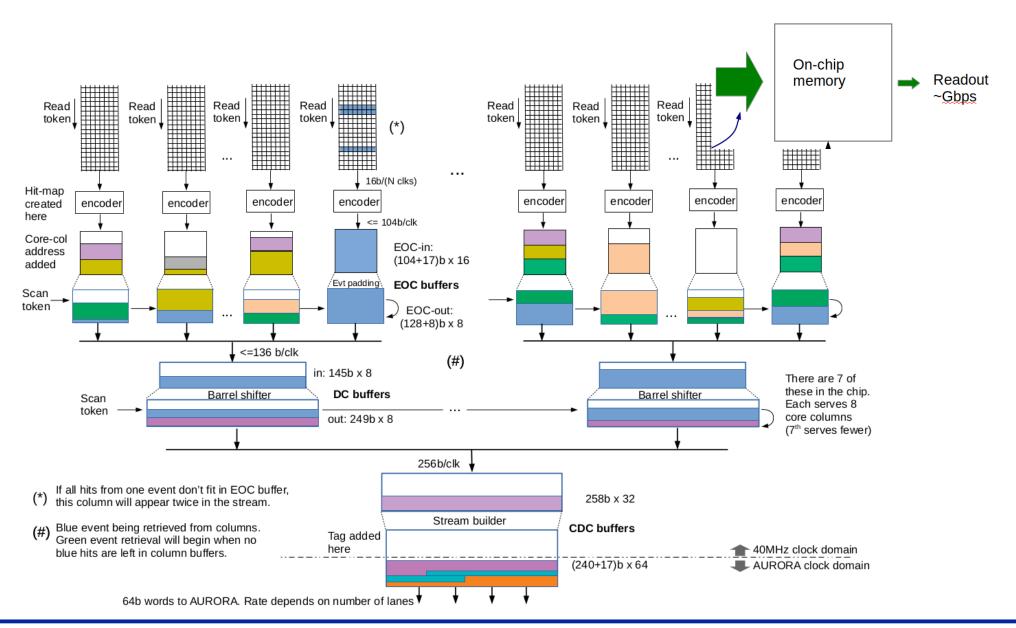

#### Complex system on chip

### Example of non-trivial processing

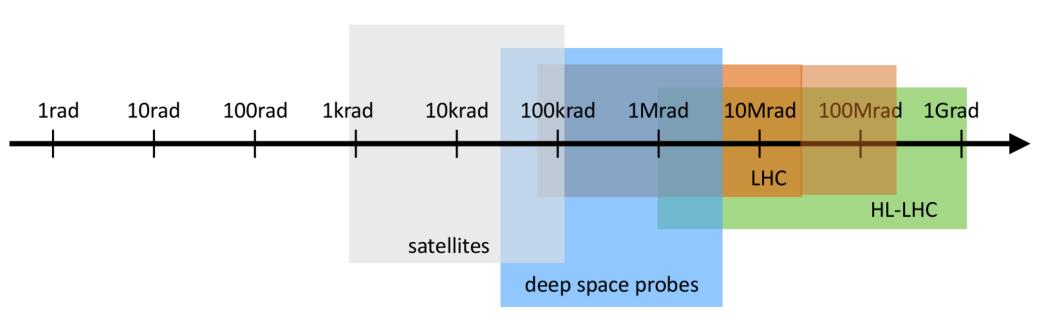

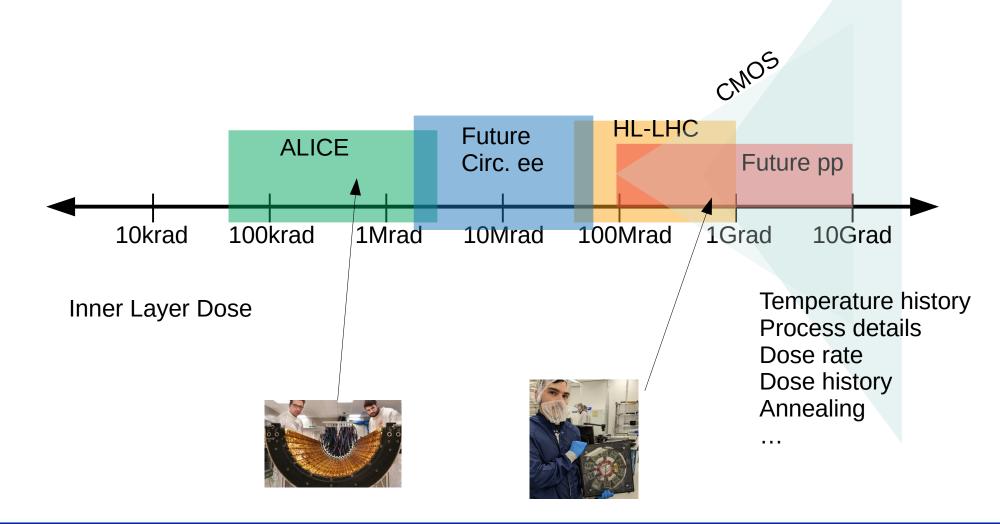

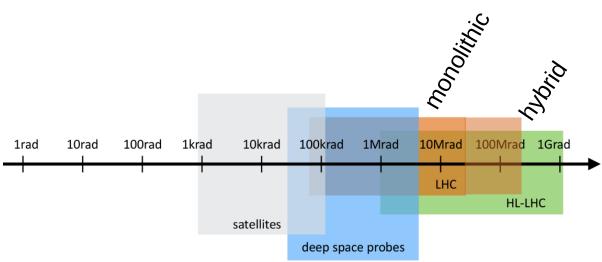

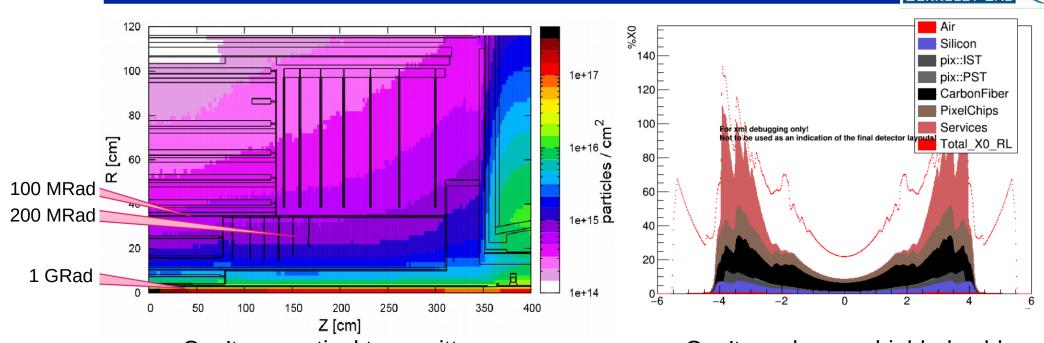

## **Radiation Environments**

#### **HEP IC Radiation Outlook**

### Trade-offs

Highly customized non-portable process

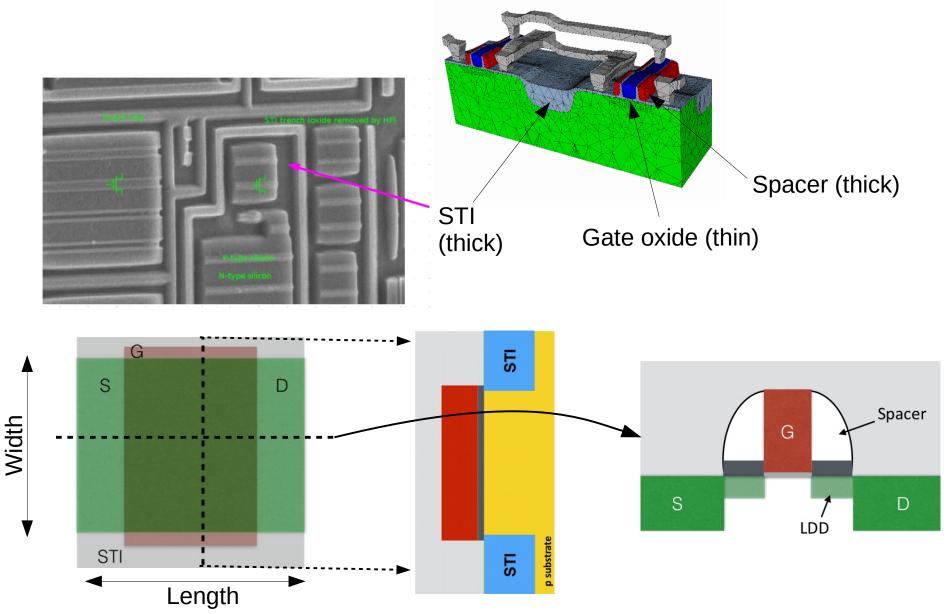

# HEP IC Electronics Radiation Damage

- Change in effective doping is <u>insignificant</u>, because doping levels in CMOS transistors are very high.

- All radiation damage effects to CMOS are due to parasitic electric fields form charge trapped in oxides and oxide-silicon interfaces

- Meet the oxides:

- Gate oxide

- Field Oxide

- Buried Oxide (only for SOI)

- Shallow trench Isolation (STI)

- **Gate Spacer**

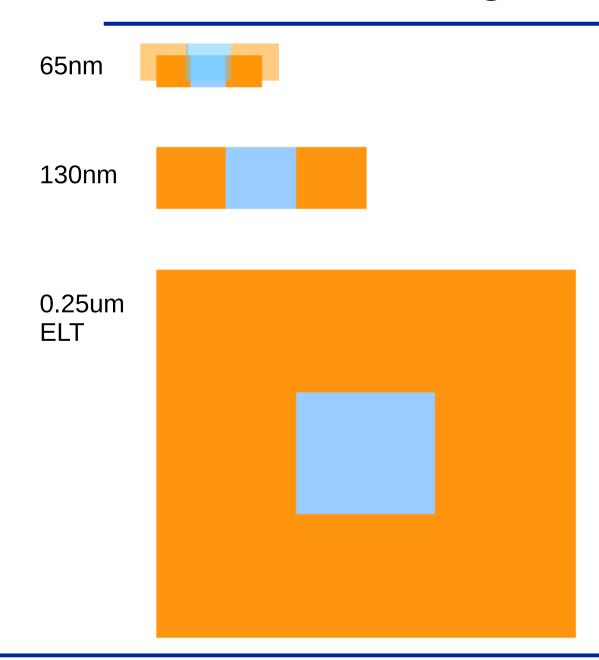

# STI, Gate, Spacer

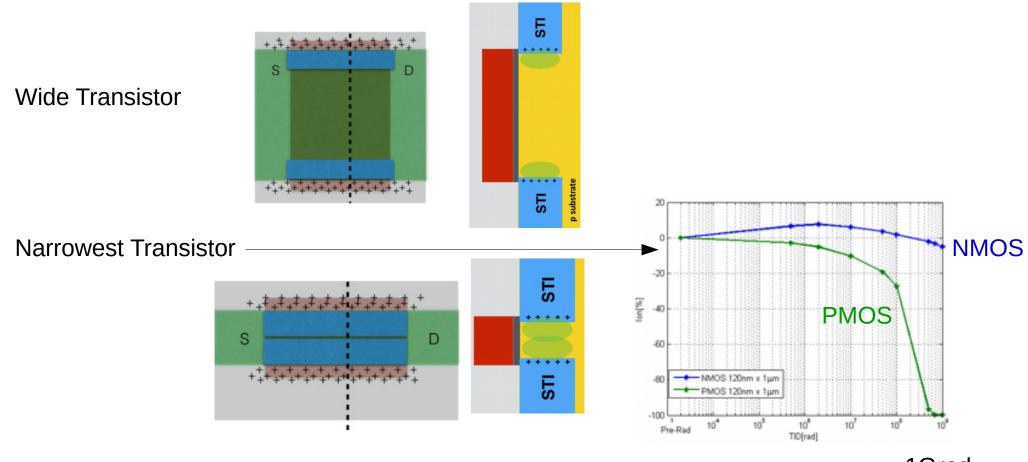

#### RINCE

#### Radiation Induced Narrow Channel Effect

F. Faccio and G.Cervelli, "Radiation induced edge effects in deep submicron CMOS transistors", IEEE Trans. Nucl. Science, Vol.52, N.6 (2005) pp.2413-2420 http://dx.doi.org/10.1109/TNS.2005.860698

1Grad

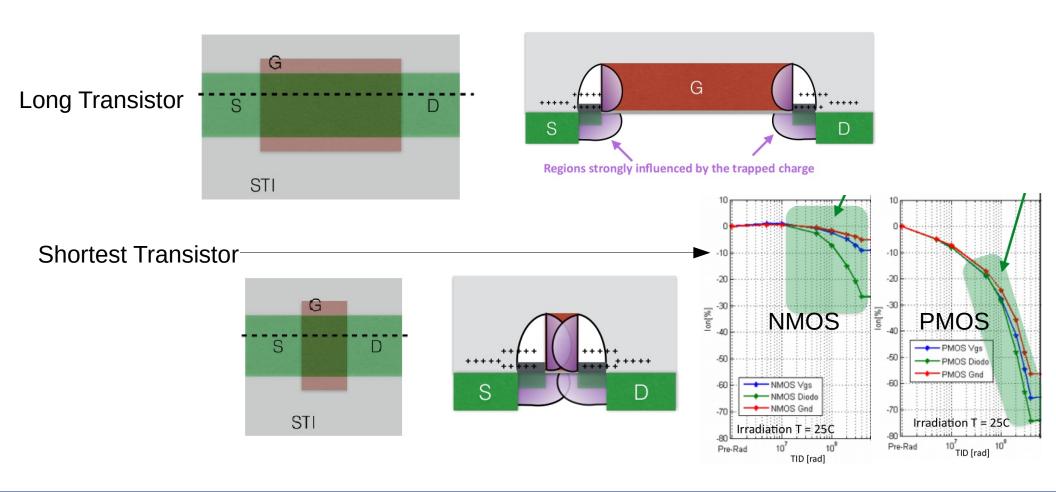

### **RISCE**

#### Radiation Induced Short Channel Effect

F. Faccio et al., "Radiation-Induced Short Channel (RISCE) and Narrow Channel (RINCE) Effects in 65 and 130 nm MOSFETs," IEEE Trans. Nucl. Science, Vol.62, N.6 (2015) http://dx.doi.org/10.1109/TNS.2015.2492778

## Recap

- Imaging particles is an inverse problem to typical imaging

- Need to surround the source of particles with senors large area of silicon needed

- Plus frame rate is in the MHz

- => Custom ICs needed

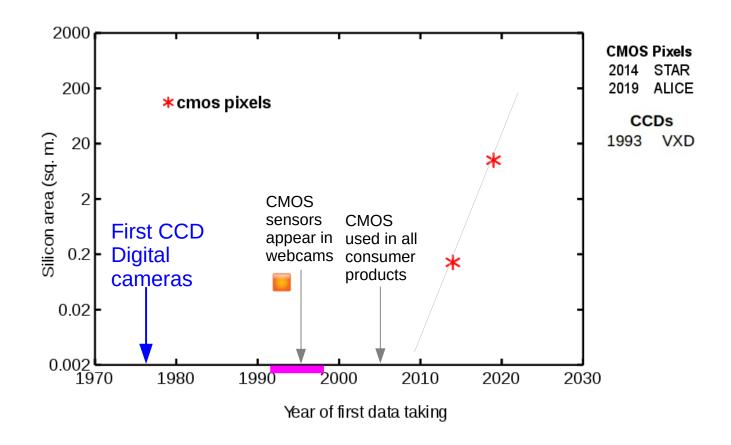

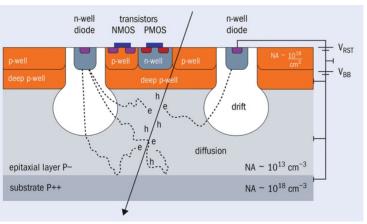

- CMOS sensors for particle detection scale better to large areas, but hae limited rate and radiation hardness and need highly customized fabrication process.

- Hybrid detectors can use standard CMOS for readout (custom design but not custom process) and radiation optimized sensors.

- Design of radiation hard ASICs is a cottage industry in HEP

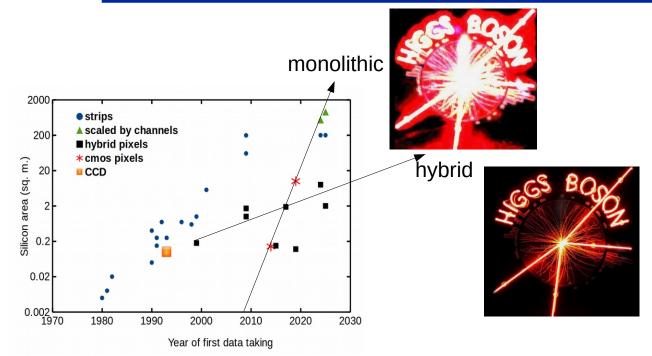

#### A future direction

#### The Rate Extremes

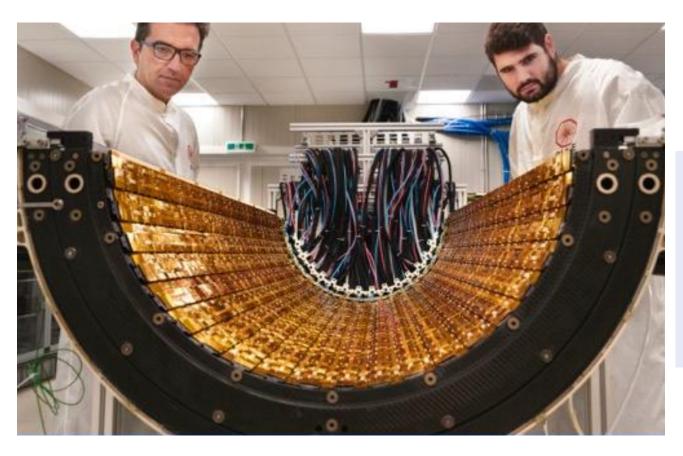

- Silicon area: 0.12 m<sup>2</sup>

- 300M pixels (20μm x 20μm)

- But only 350,000 Z decays recorded

▲ scaled by channel

■ hybrid pixels

=> most pixels were never hit by real collision particle!

#### HL-LHC

Inner layers of ATLAS and CMS high luminosity upgrades will see 10 collision particles in every Si atom!

$X 10^{16}$

#### BACKUP

#### Connection to Consumer Electronics

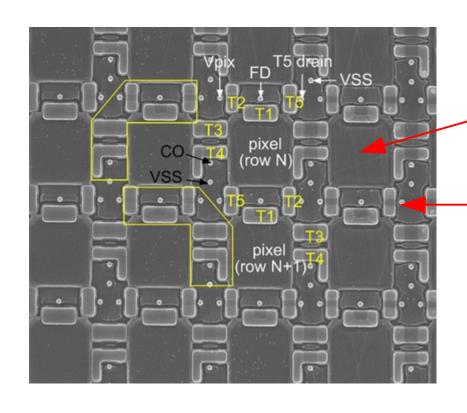

## HEPT Close-up of CMOS camera sensor

Photodiode covers about half the pixel area in this example

Metal traces have been removed. They run over the transistors leaving photodiode exposed

For particle tracking need 100% fill factor

Need low enough noise that can detect a single particle

Need radiation hardness

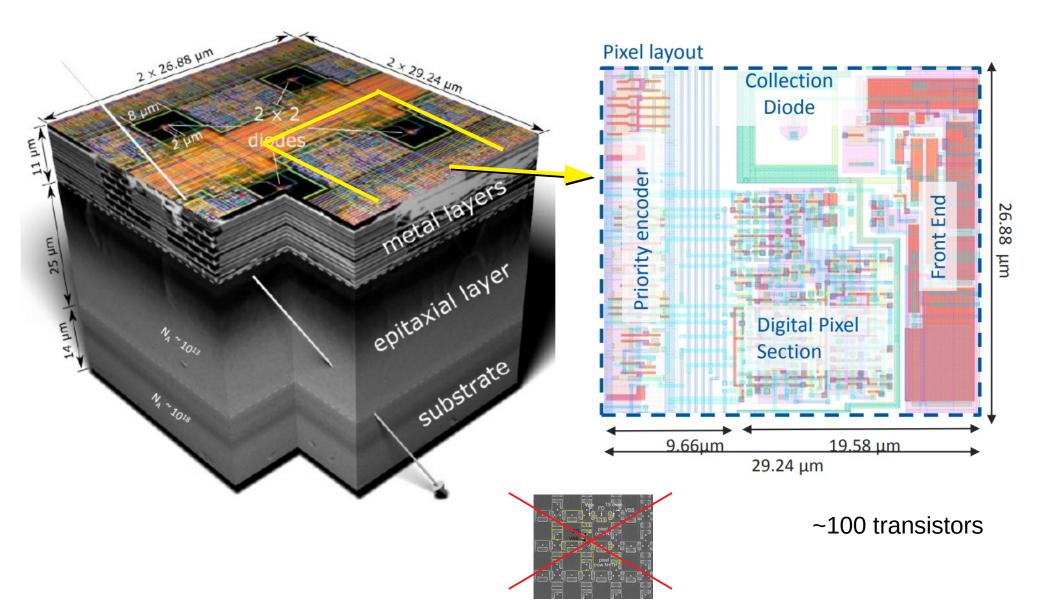

# ALICE just installed a 10m<sup>2</sup> tracker made of CMOS sensors

Highly customized CMOS process. Proprietary. Not portable

#### ALPIDE sensor chip- not a simple 3T pixel

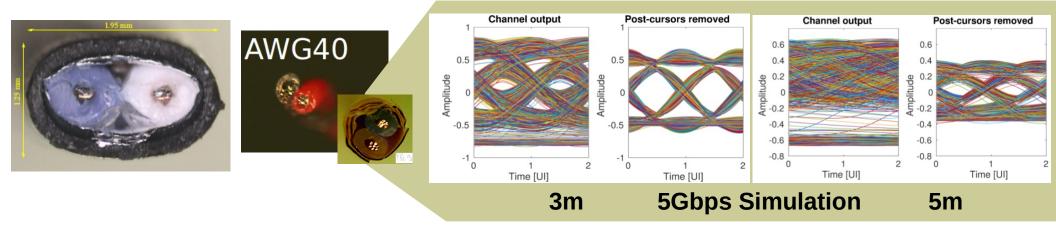

#### Limited Readout Bandwidth

Can't use optical transmitters

Can't use heavy shielded cables

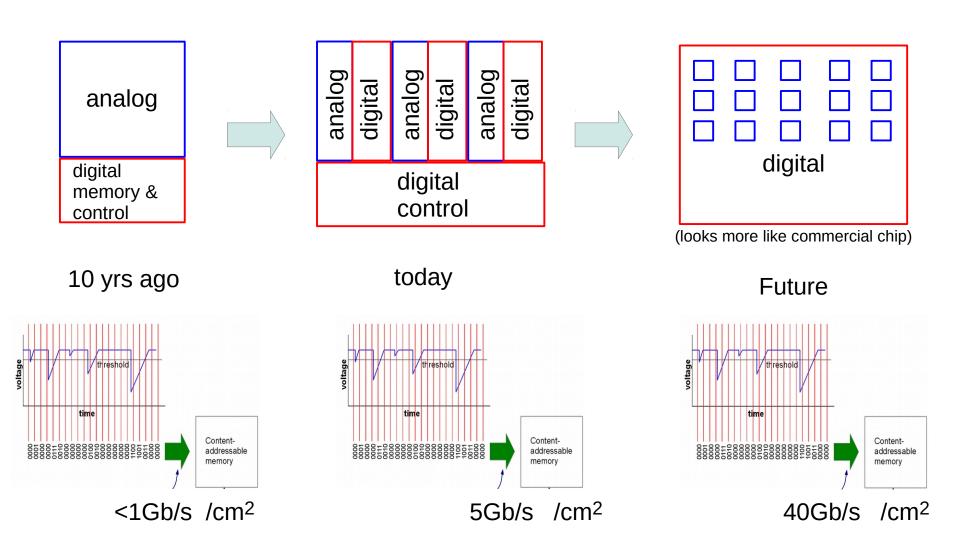

## Readout Chip Evolution

## What Images Look Like

## Rad Hard Logic Density Scaling

## FE-I4 Digital Region

Digital block is shared with 4 inputs- each form an identical analog pixel.

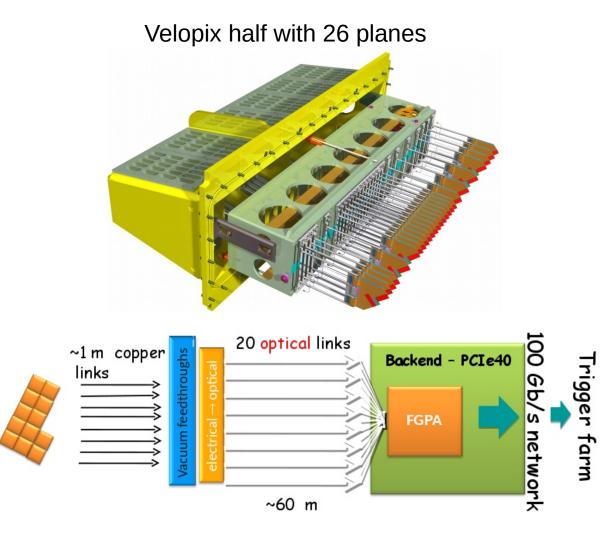

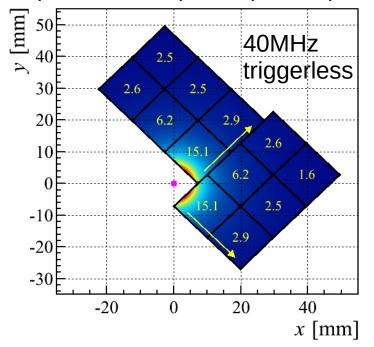

### Velopix triggerless readout

#### Readout chips in LHCb Velopix plane Output data rate per chip in Gbps

- Geometry looks like data flow diagram

- Lots of room outside physics acceptance

- Can have many cables out of each chip