### **Silicon Tracking Detectors**

M. Garcia-Sciveres Lawrence Berkeley National Lab

2022 HEPIC Summer Week – SLAC

Close-up of ATLAS pixel detector, installed in 2007

- Imaging particles

- Pixel detector technology

- High rate challenges

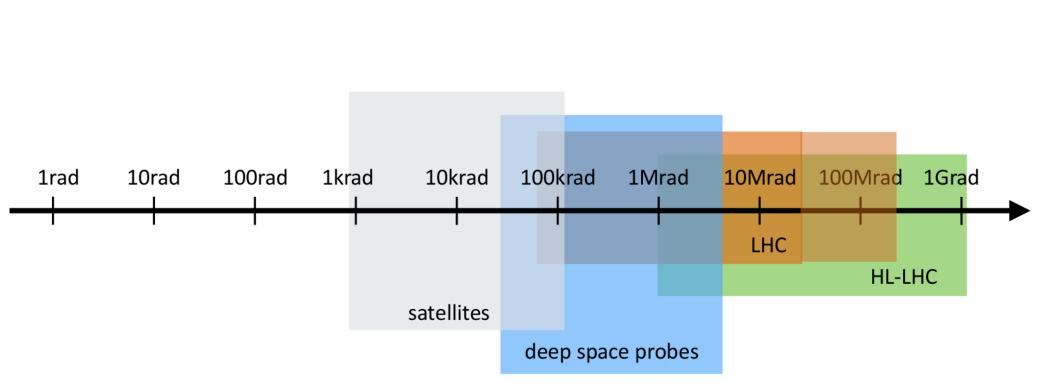

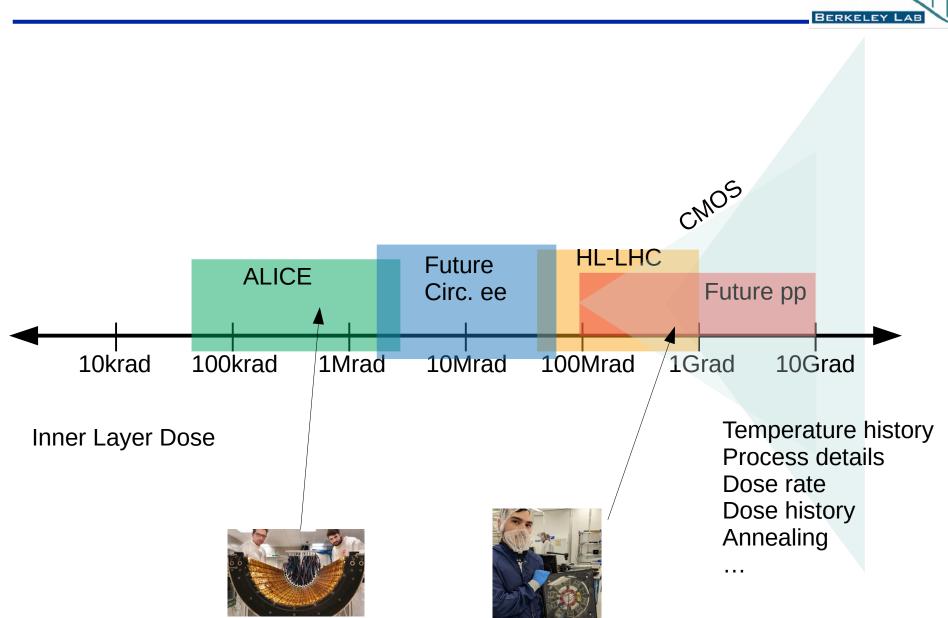

- ASIC Radiation damage

- Summary

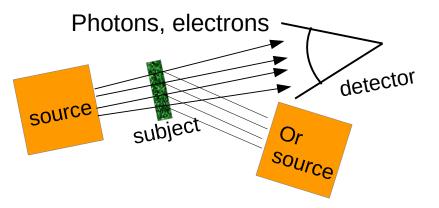

## **Imaging Particles**

Source

subject

and

High energy charged particles

detector

(tracker)

detector

detector

- What you're used to:

- Detector to completely stops photons

- Lots of photons- every pixel gets some- source intensity limited on purpose

- Integrate or count many photons per channel

- Crucial differences for Imaging high energy charged particles

- Want particles to pass thorough imaging detector (aka tracker) as if it was not there. There are other detectors behind it

- There is no sample. We are looking at the quantum vacuum. Want intensity as high as possible.

- Measure every particle individually

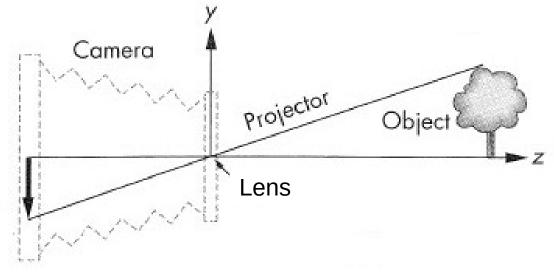

## Inverse problem to usual imaging

.....

BERKELEY

lin)

\_AB

## Inverse problem to usual imaging

#### Silicon Trackers – M. Garcia-Sciveres

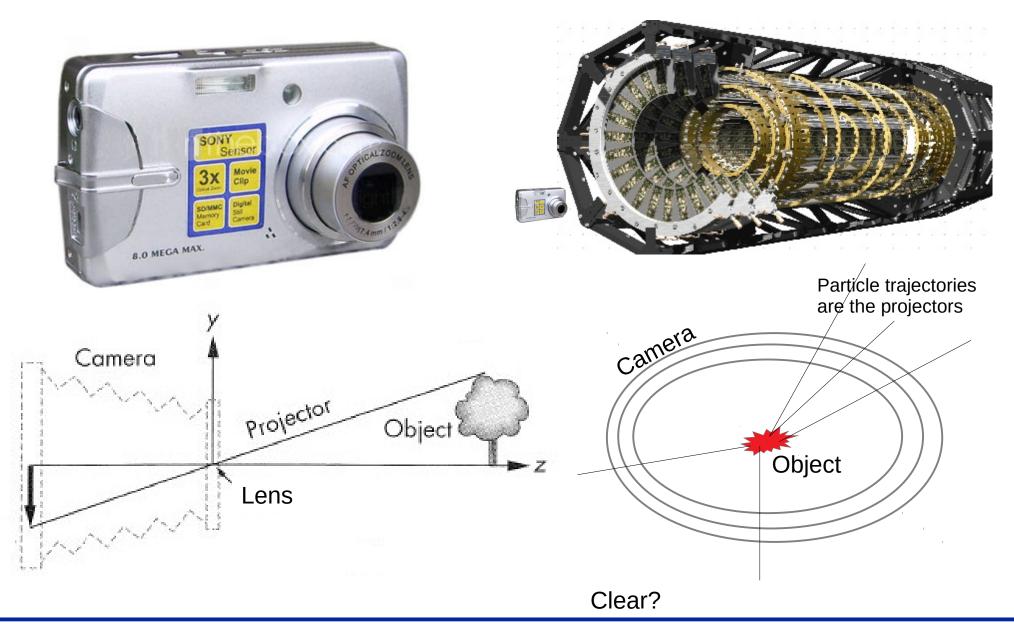

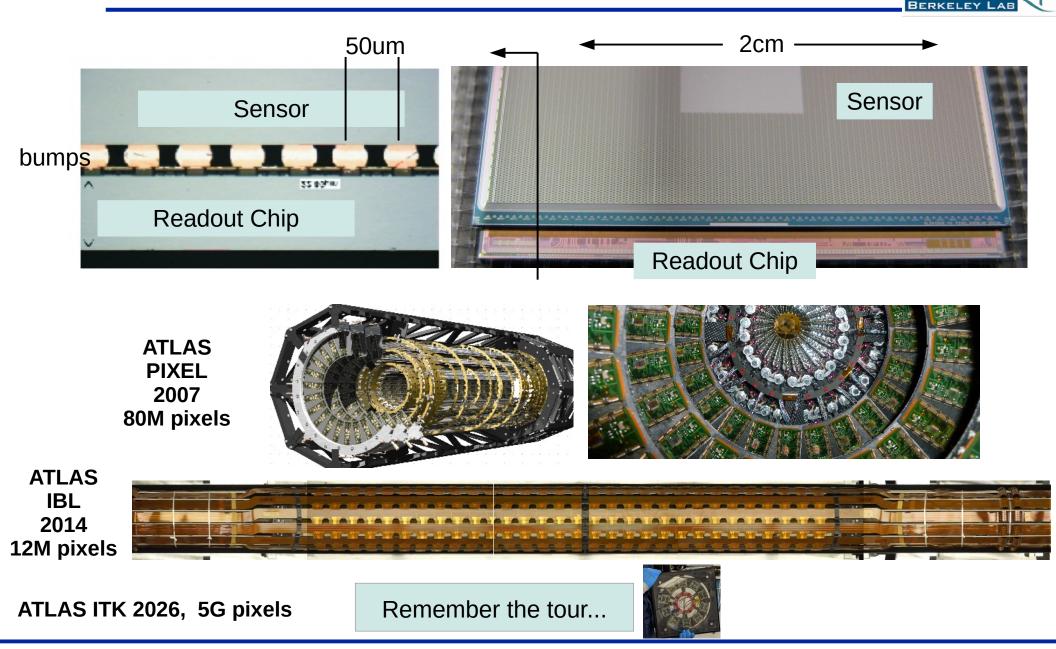

### Let's build ourselves a silicon pixel tracking detector

## Let's do it

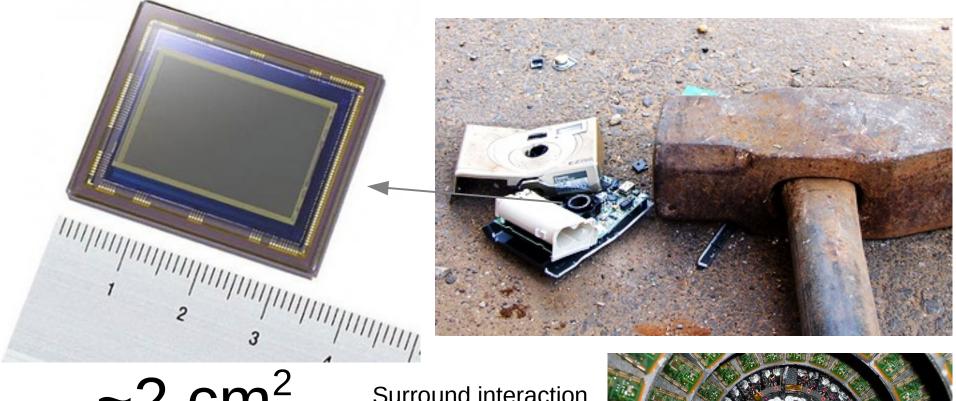

~2 cm<sup>2</sup>

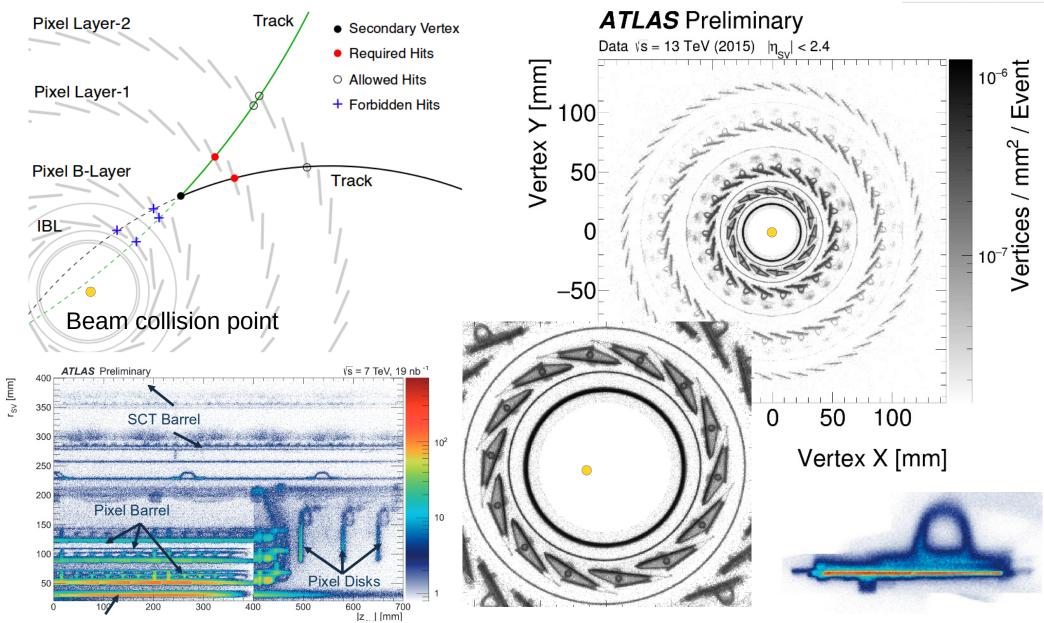

Surround interaction point with few layers of sensors

~100 000 cm<sup>2</sup>

(\$500K plus tax)

## Will it work?

• OK, so this thing can do 30 fps right?

- Then instead of 50,000 sensors we need ( 40,000,000 / 30 ) \* 50,000 = 65B sensors, which will only cost us \$650B. Maybe we can get a volume discount?

- - •

- •

- And that's why we need custom ASICs to make tracking detectors

- Review how they're actually made next (or just remember the tour)

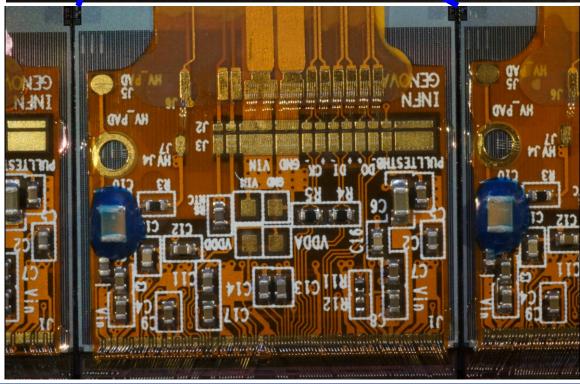

## Hybrid Pixel Detector Technology

.....

IIII

## Hybrid Pixel Technology (IBL)

#### ATLAS beam pipe layer (IBL)

- Radiation dose: 5x10<sup>15</sup> n\_eq/cm<sup>2</sup>

- "Frame rate": 40 MHz

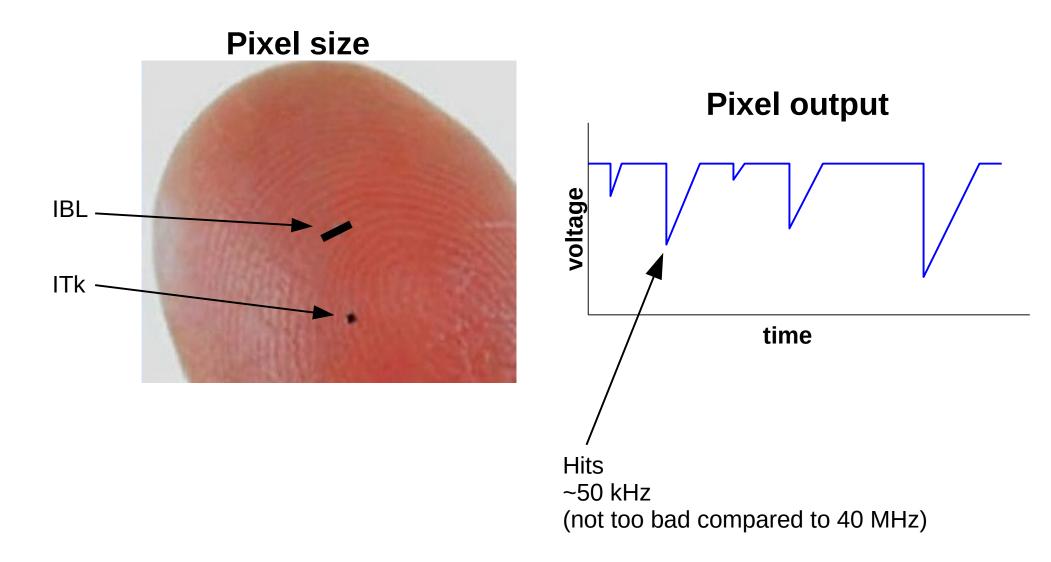

- Pixel size: 50μm x 250μm

- Silicon area: 0.15 m<sup>2</sup>

## Detector can image itself in 3D

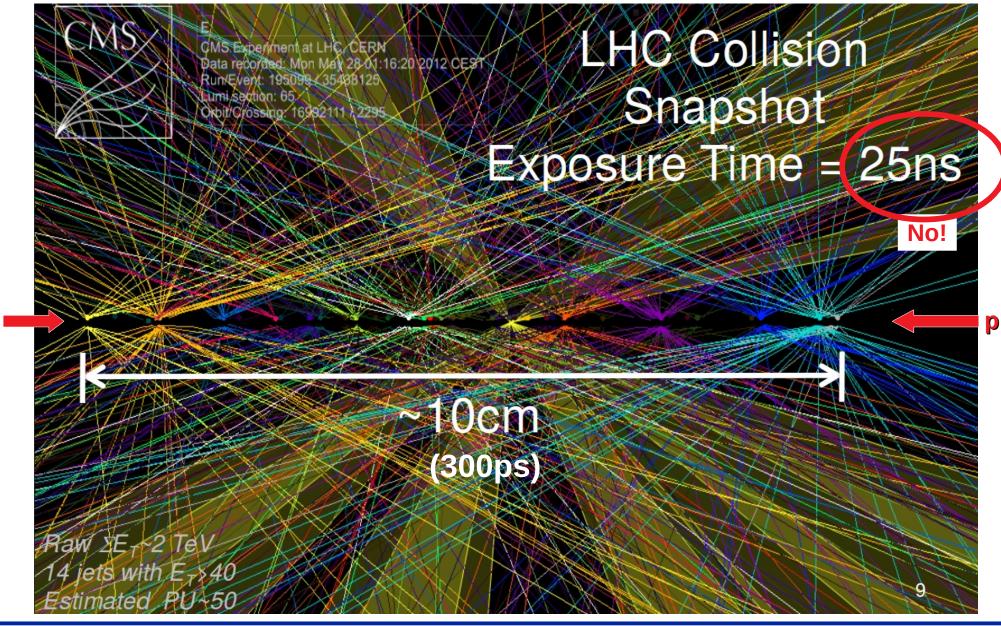

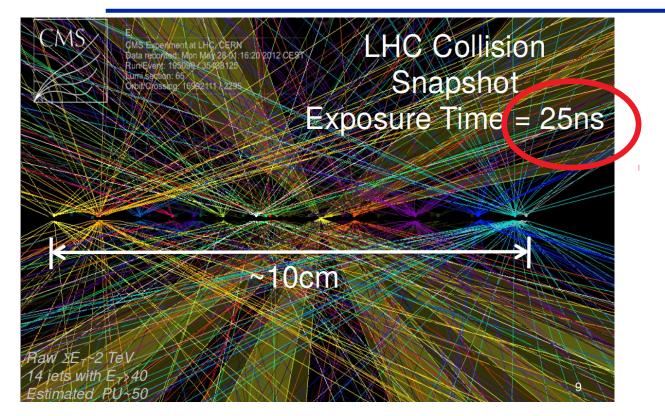

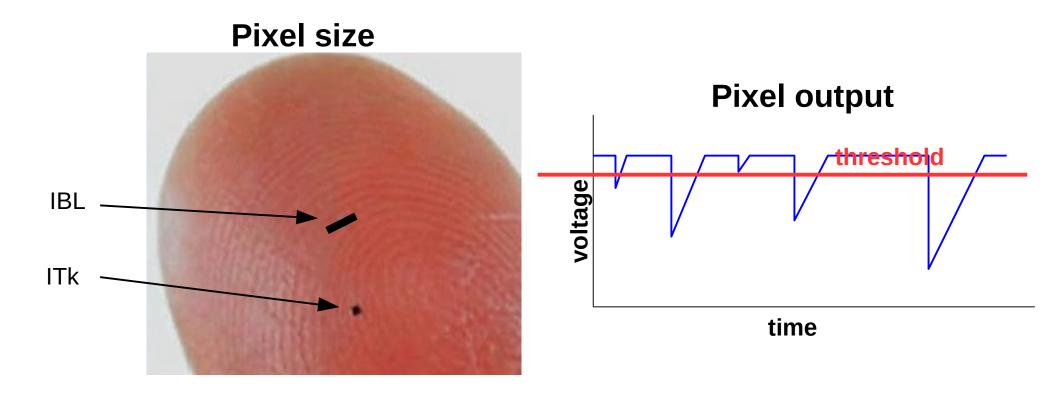

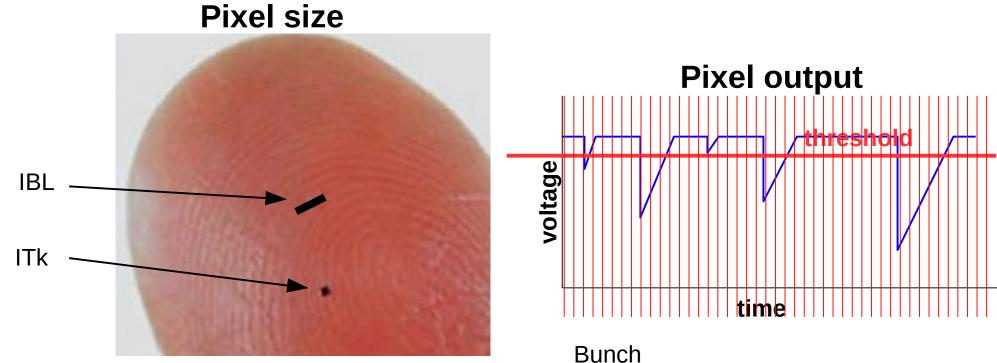

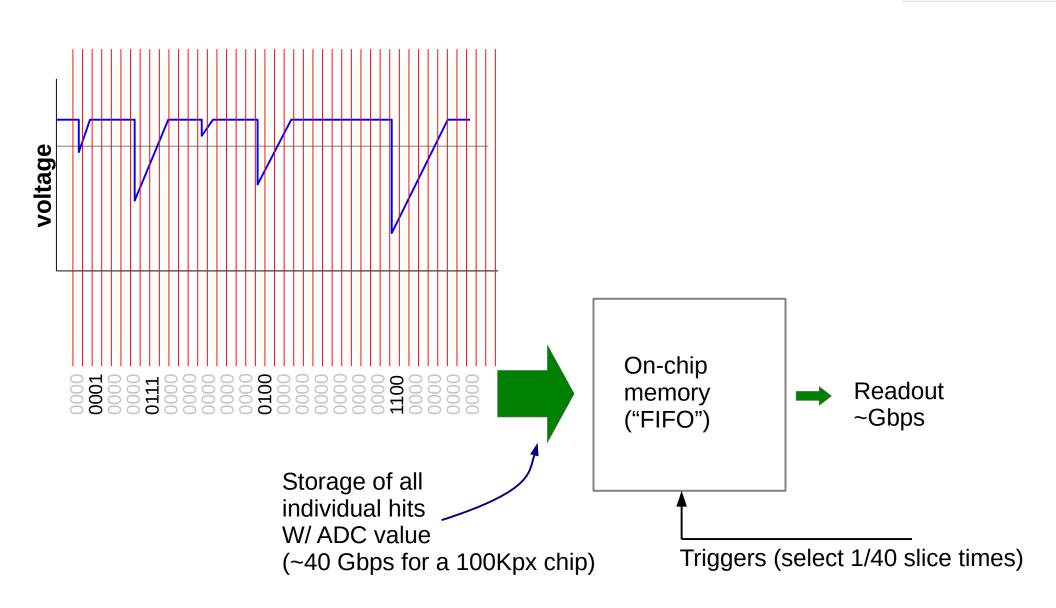

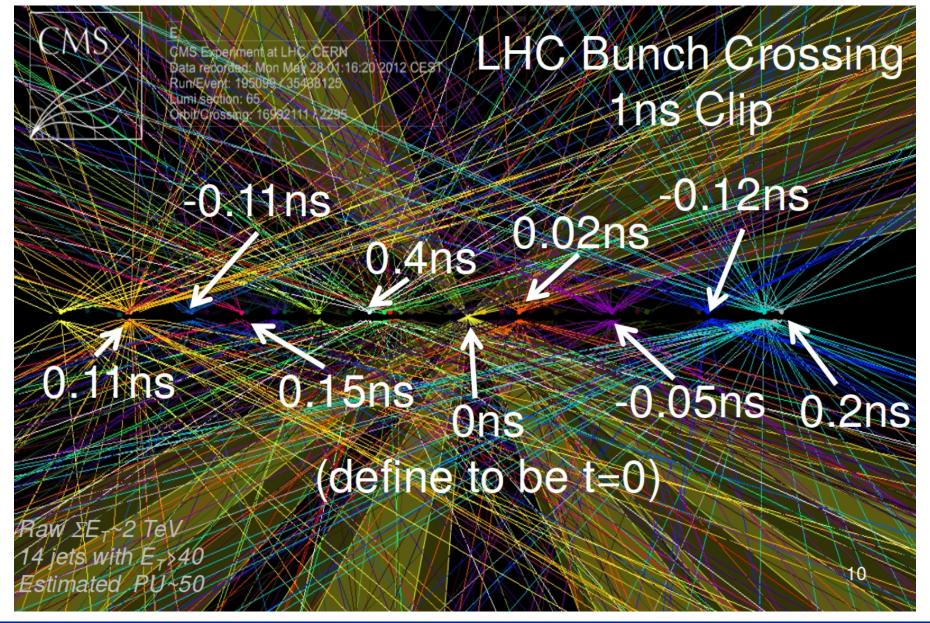

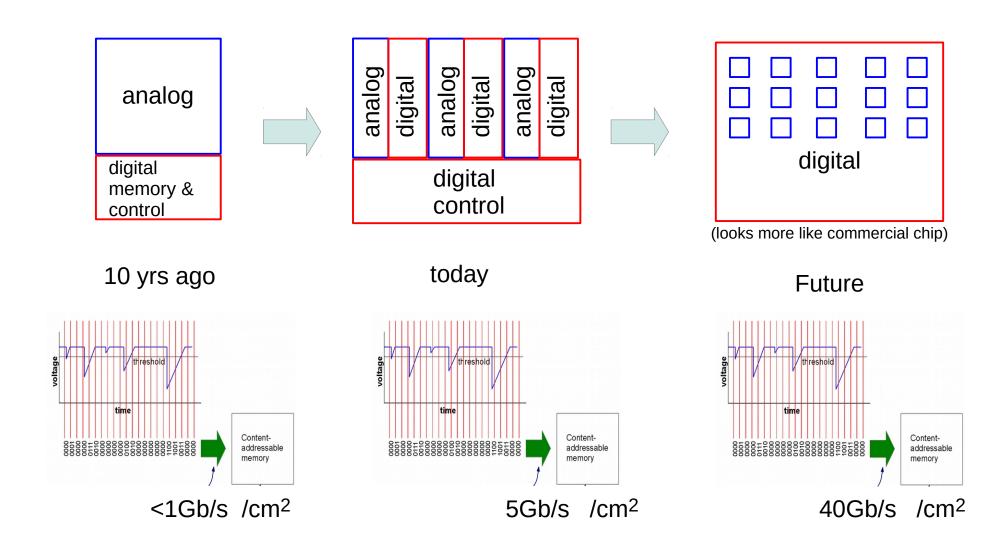

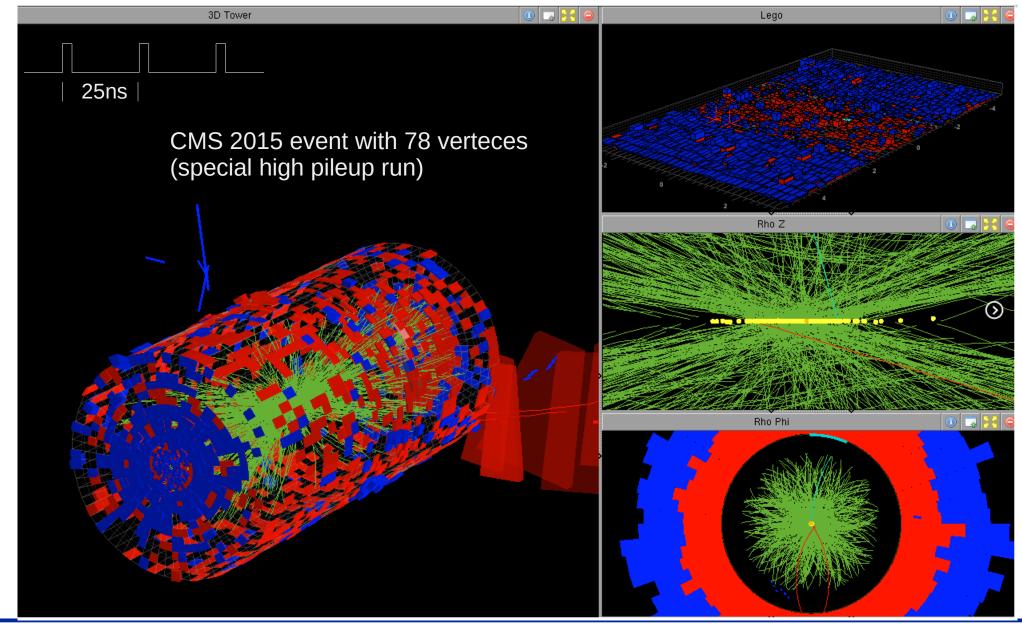

## But how do we handle the rate?

- Capturing 40M 5Gpixel images per second is not feasible.

- Triggering only saves a factor of 40 in readout

- 1M 5Gpixel images per second is still far from feasible

- A: We do NOT do conventional image capture.

- We treat every pixel as an independent, free-running detector and store it's output (heavily redacted)

crossings

Digitize amplitude above threshold in each Bunch Crossing

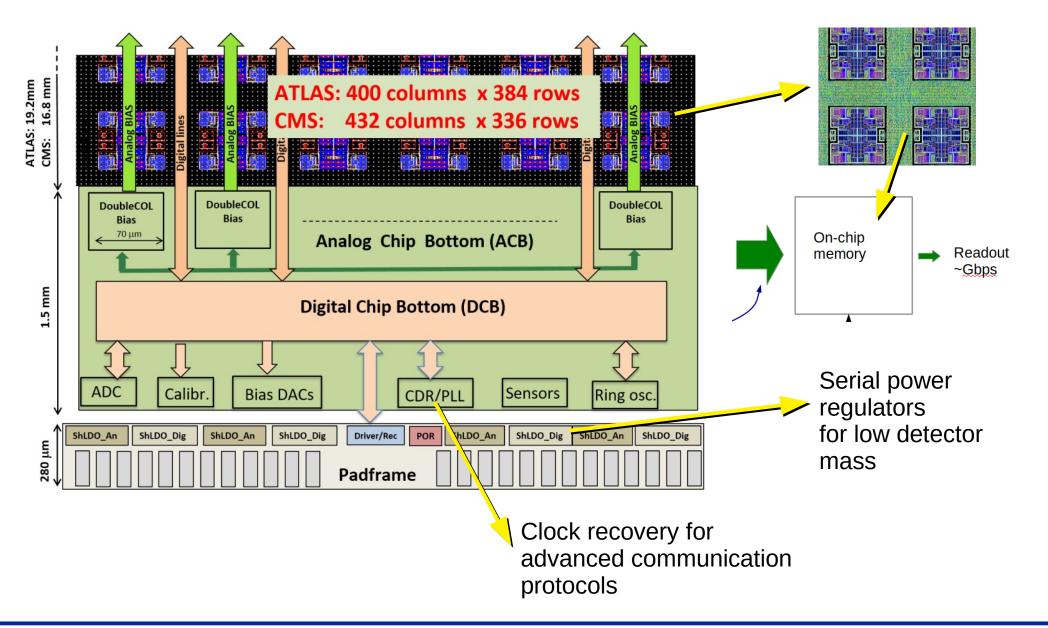

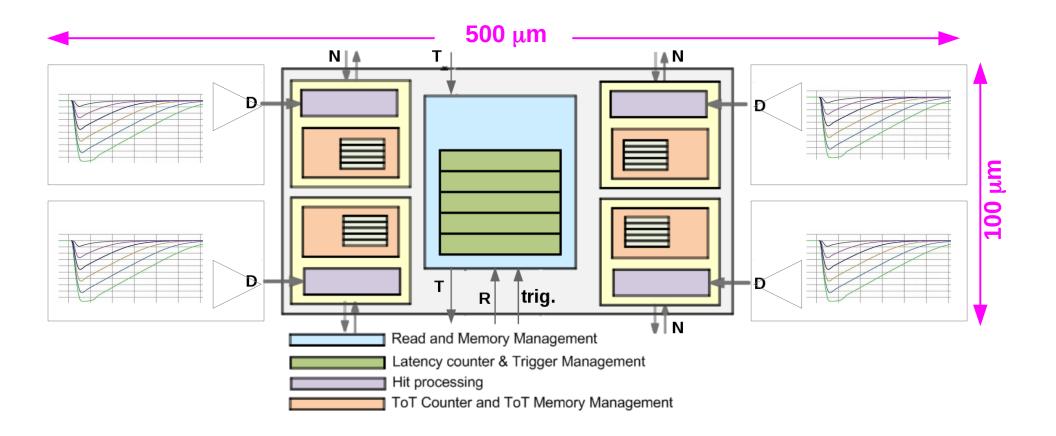

## **On-Chip Storage and Trigger**

IIIÌ

BERKELEY

BERKELEY LAB

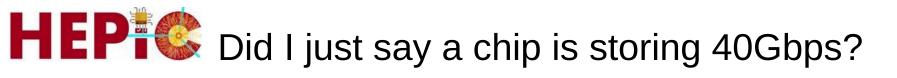

High rate pixel readout chips are memories (in addition to being pixel readout chips)

Figure 2. DDR4 higher performance compared with DDR3L and DDR2

(and this is not rad hard)

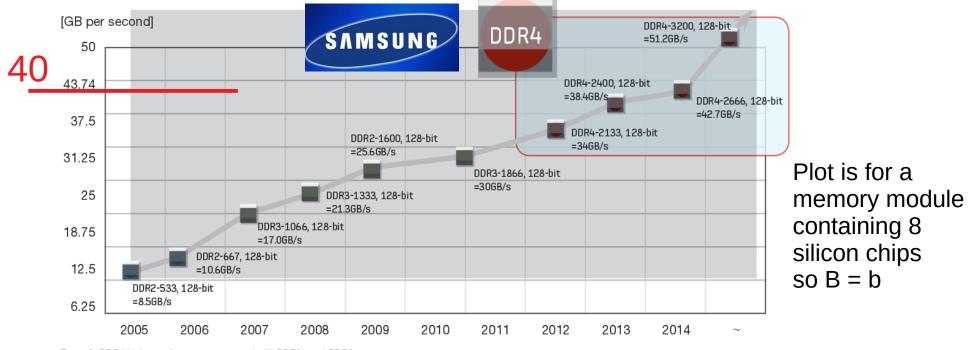

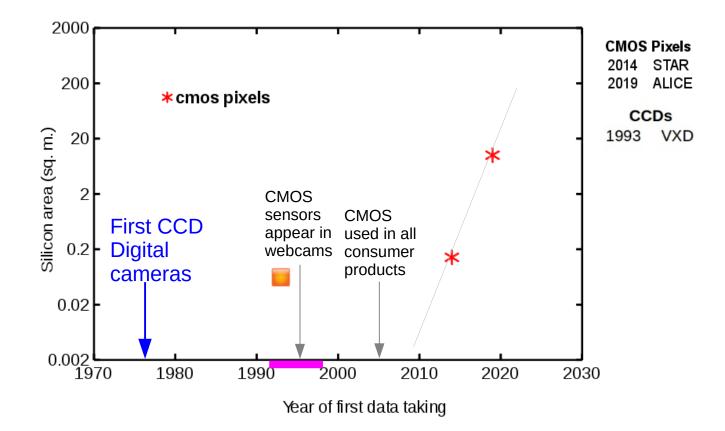

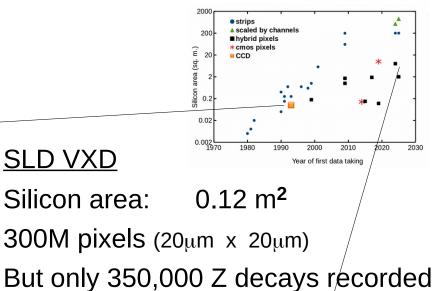

## Silicon Detectors at Colliders

(and in orbit)

Silicon Trackers – M. Garcia-Sciveres

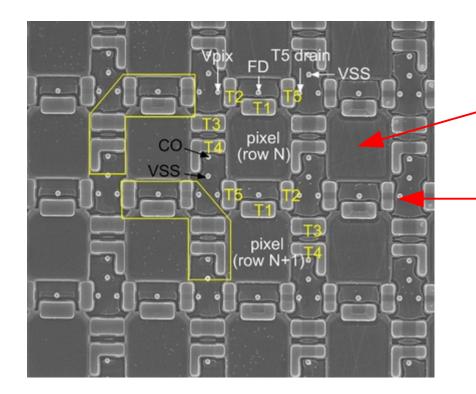

# HEP Close-up of CMOS camera sensor

Photodiode covers about half the pixel area in this example

Metal traces have been removed. They run over the transistors leaving photodiode exposed

rrrr

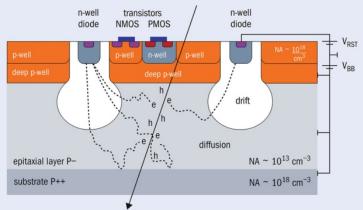

For particle tracking need 100% fill factor

Need low enough noise that can detect a single particle

Need radiation hardness

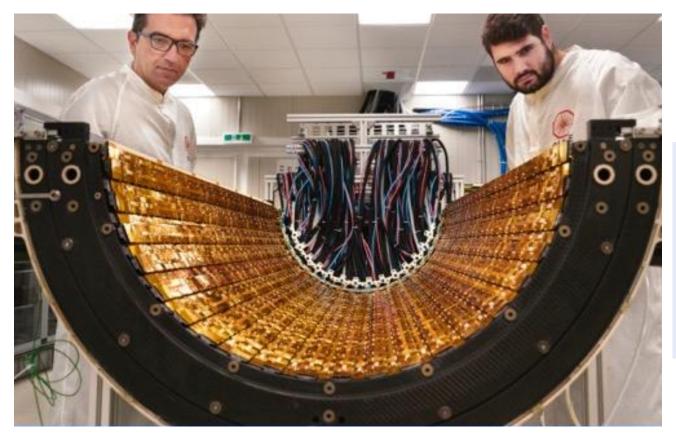

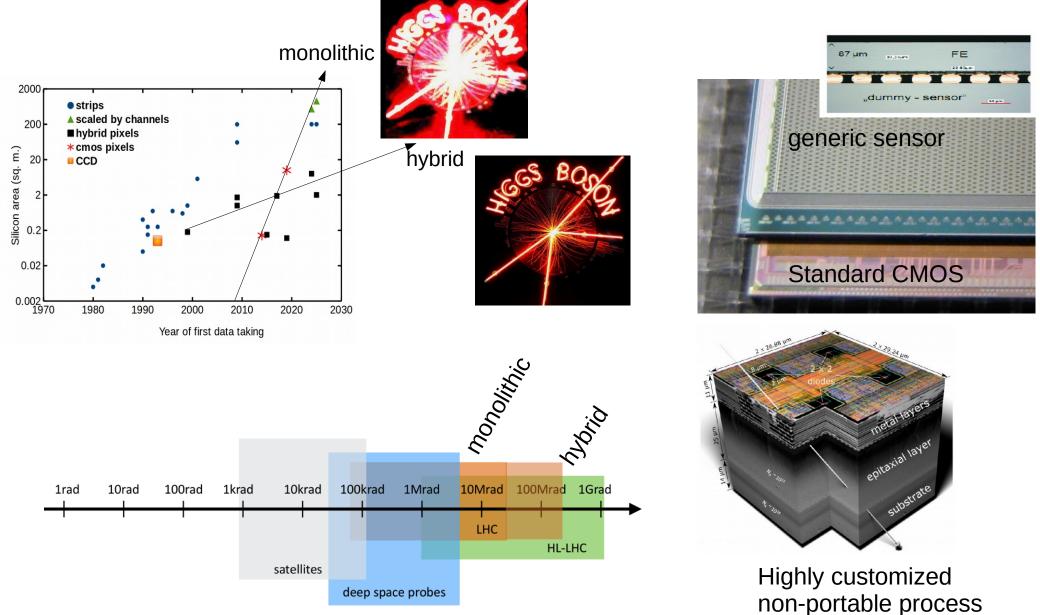

# ALICE just installed a 10m<sup>2</sup> tracker made of CMOS sensors

Highly customized CMOS process. Proprietary. Not portable

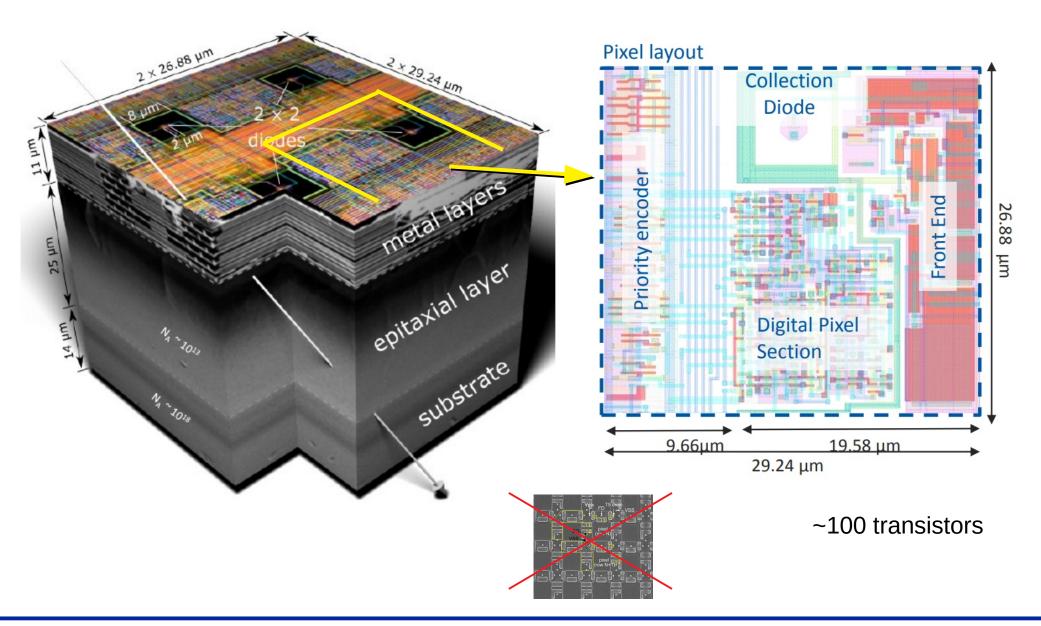

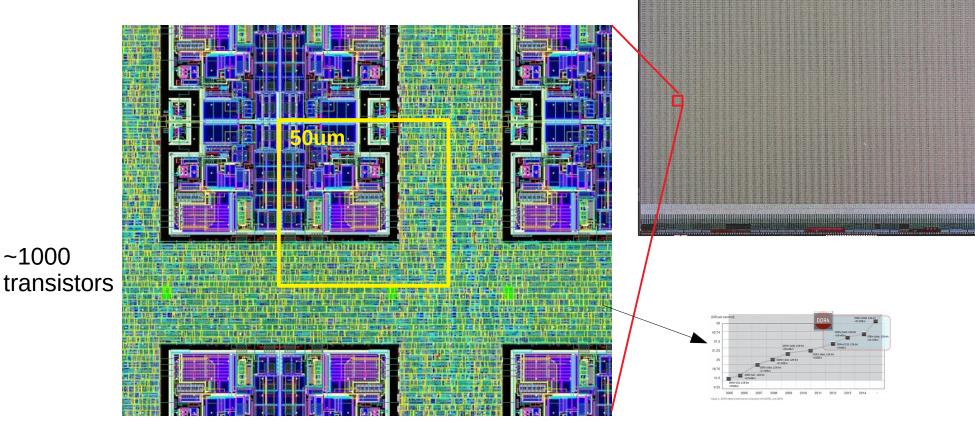

# RD53 Hybrid Pixel Readout 100x higher rate and radiation

#### Cern.ch/rd53

**RD-53 Collaboration Home**

RD-53 will design and produce the next generation of readout chips for the ATLAS and CMS pixel detector upgrades at the HL-LHC. More details can be found in the 2018 extension proposal and the original collaboration proposal.

$\sim 1000$

Complex system on chip

## Example of non-trivial processing

On-chip Readout memory ~Gbps ₿ Read Read Read Read Read Read Read token token token token token. token token (\*) ... . . . . . . 16b/(N clks) Hit-map encoder encoder encoder encoder encoder encoder encoder encoder created here <= 104b/clk Core-col EOC-in: address (104+17)b x 16 added Evt padding EOC buffers Scan token EOC-out: (128+8)b x 8 <=136 b/clk (#) in: 145b x 8 There are 7 of these in the chip. DC buffers Barrel shifter Barrel shifter Scan Each serves 8 token core columns out: 249b x 8 (7th serves fewer) 256b/clk If all hits from one event don't fit in EOC buffer, this column will appear twice in the stream. (\*) 258b x 32 Stream builder Blue event being retrieved from columns. Green event retrieval will begin when no CDC buffers (#) Tag added here 40MHz clock domain blue hits are left in column buffers. (240+17)b x 64 AURORA clock domain 64b words to AURORA. Rate depends on number of lanes

#### Silicon Trackers – M. Garcia-Sciveres

IIIÌ

LAE

rrr

BERKELEY

### Large design effort (top end of the scale for HEP)

**m**

**rrrr**

BERKELEY LAB

IIIÌ

**rrrr**

Trade-offs

Silicon Trackers – M. Garcia-Sciveres

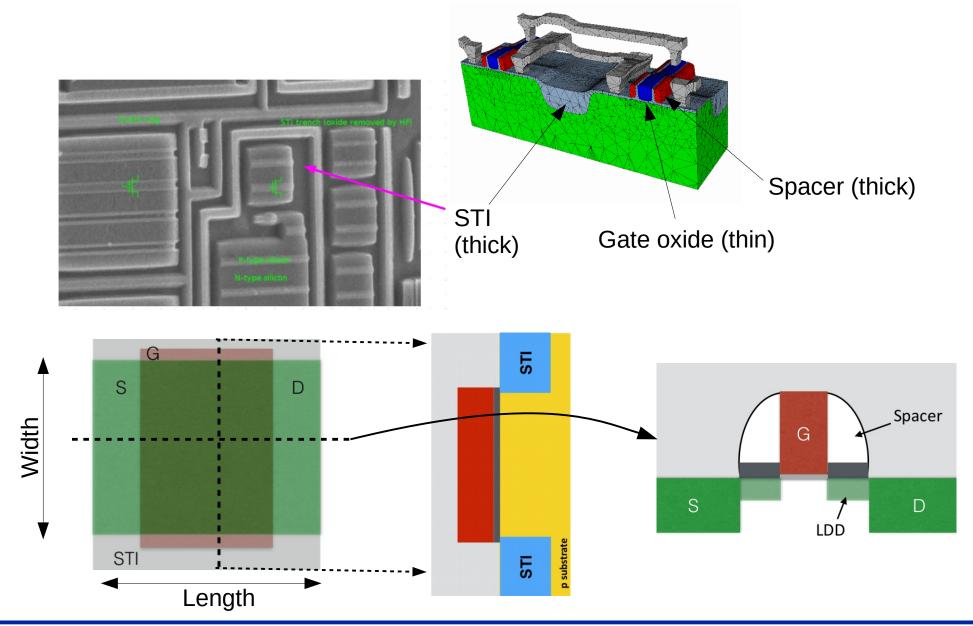

# • Change in effective doping is <u>insignificant</u>, because doping levels in CMOS transistors are very high.

**HEP** IC Electronics Radiation Damage

- All radiation damage effects to CMOS are due to parasitic electric fields form charge trapped in oxides and oxide-silicon interfaces

- Meet the oxides:

- Gate oxide

- Field Oxide

- Buried Oxide (only for SOI)

- Shallow trench Isolation (STI)

- Gate Spacer

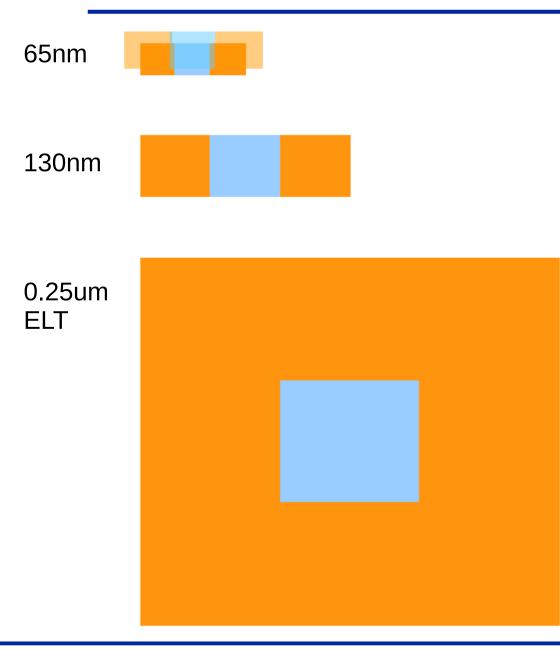

## STI, Gate, Spacer

RINCE

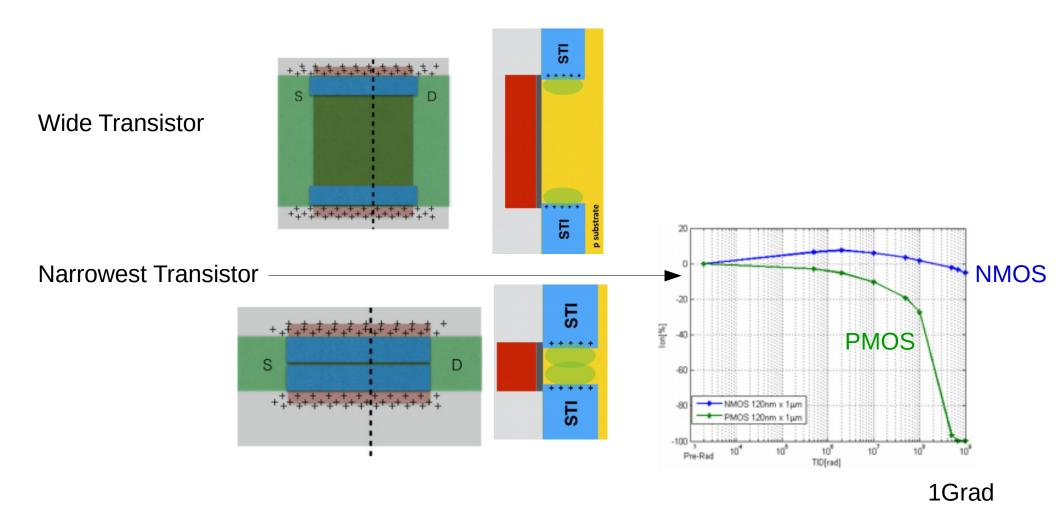

#### **Radiation Induced Narrow Channel Effect**

F. Faccio and G.Cervelli, "Radiation induced edge effects in deep submicron CMOS transistors", IEEE Trans. Nucl. Science, Vol.52, N.6 (2005) pp.2413-2420 http://dx.doi.org/10.1109/TNS.2005.860698

RISCE

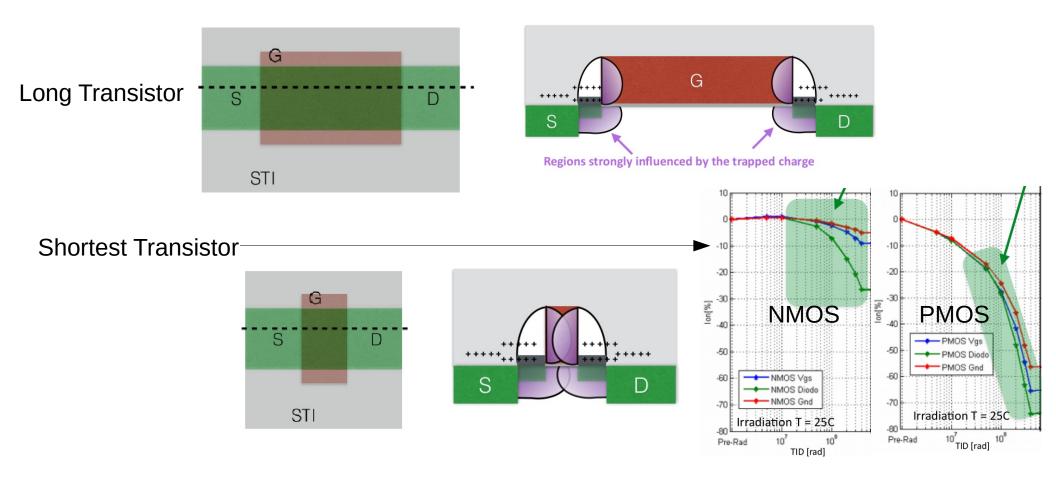

#### **Radiation Induced Short Channel Effect**

F. Faccio et al., "Radiation-Induced Short Channel (RISCE) and Narrow Channel (RINCE) Effects in 65 and 130 nm MOSFETs," IEEE Trans. Nucl. Science, Vol.62, N.6 (2015) http://dx.doi.org/10.1109/TNS.2015.2492778

Recap

- Imaging particles is an inverse problem to typical imaging

- Need to surround the source of particles with senors large area of silicon needed

- Plus frame rate is in the MHz

- => Custom ICs needed

- CMOS sensors for particle detection scale better to large areas, but hae limited rate and radiation hardness and need highly customized fabrication process.

- Hybrid detectors can use standard CMOS for readout (custom design but not custom process) and radiation optimized sensors.

- Design of radiation hard ASICs is a cottage industry in HEP

## A future direction

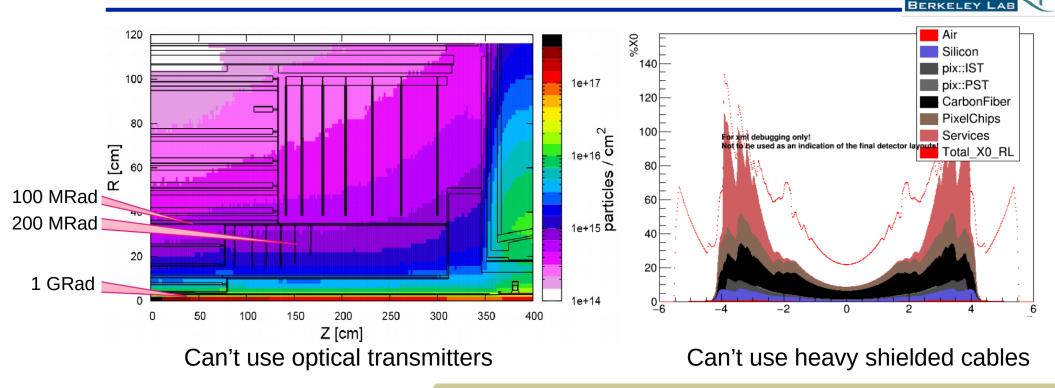

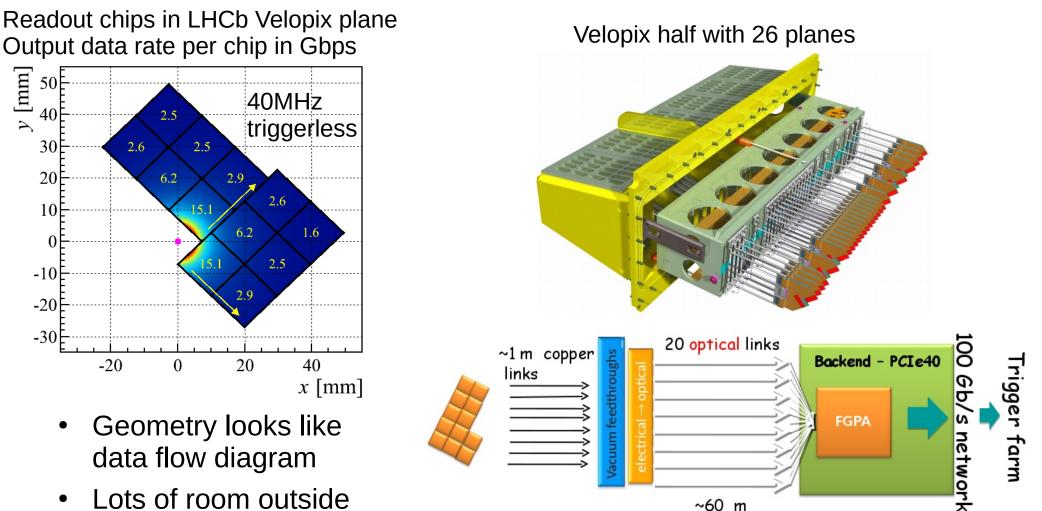

## The Rate Extremes

=> most pixels were never hit by real collision particle!

### <u>HL-LHC</u>

Inner layers of ATLAS and CMS high luminosity upgrades will see 10 collision particles in every Si atom!

## BACKUP

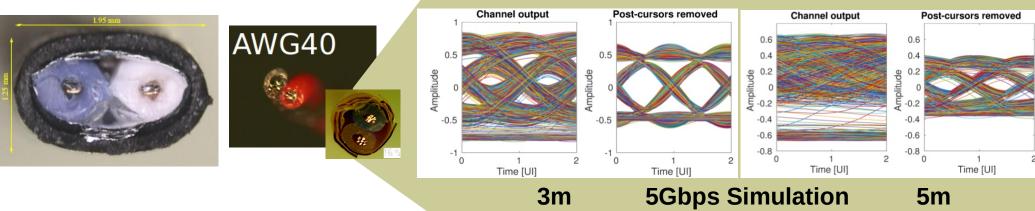

## Limited Readout Bandwidth

IIIÌ

**rrrr**

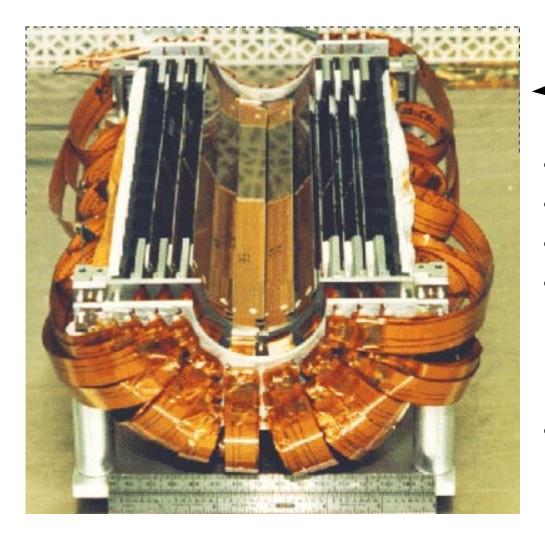

**Readout Chip Evolution**

IIIÌ

LAB

**rrrr**

BERKELEY

## What Images Look Like

Silicon Trackers – M. Garcia-Sciveres

## Rad Hard Logic Density Scaling

Digital block is shared with 4 inputs- each form an identical analog pixel.

# Velopix triggerless readout

Can have many cables out of each chip

physics acceptance