# SVT DAQ Setup @ SLAC

06/20/2021

### Outline

#### Introduction

- SVT DAQ Overview

- Some inspiration taken from <u>Cam's Collab 2019 Talk</u>

- DAQ Setup at SLAC

- Architecture schematics

- Hardware components

- Back-end setup: current status

- Local Data taking

- Feb testing

- Integration in jLab system

- Integration with CODA and Epics

- Slow Control integration / Monitoring integration

- Next steps and plans

SLAO

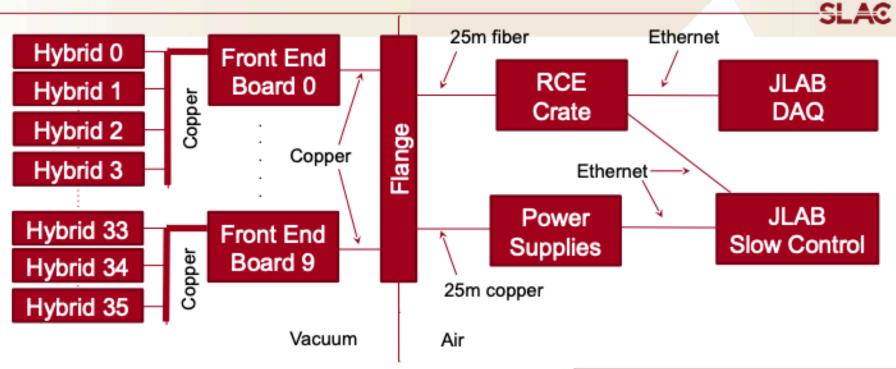

# **SVT DAQ Overview**

- 36 hybrids

- 12 in layers 0 3 (2 per module)

- 24 in layers 4 6 (4 per module)

- 10 front end boards

- 4 servicing layers 0 3 with 4 hybrids per board

- 6 servicing layers 4 6 with 4 hybrids per board

- RCE crate: ATCA, data reduction, event building and JLab DAQ interface

| Naw Abo data late (Obps) |      |  |  |  |  |

|--------------------------|------|--|--|--|--|

| Per hybrid               | 3.33 |  |  |  |  |

| Per L1-3 Front end board | 10   |  |  |  |  |

| Per L4-6 Front end board | 13   |  |  |  |  |

Raw ADC data rate (Ghns)

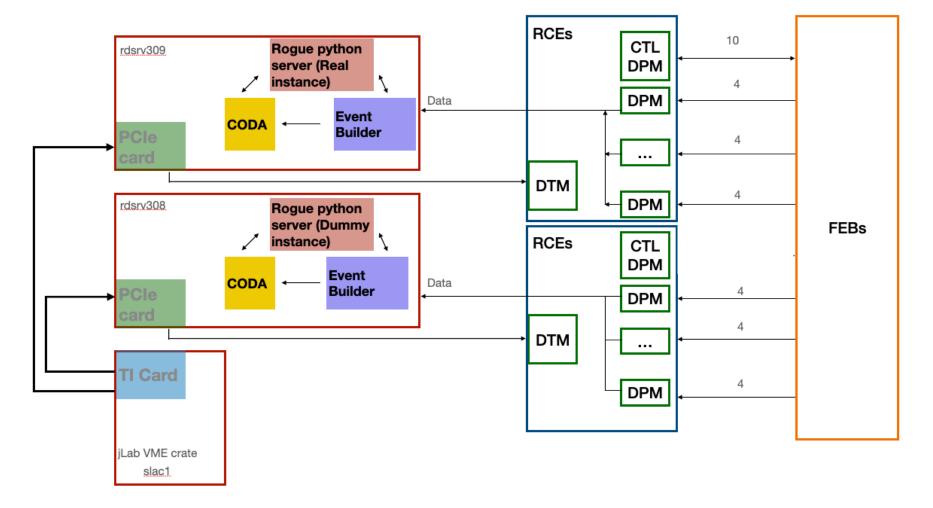

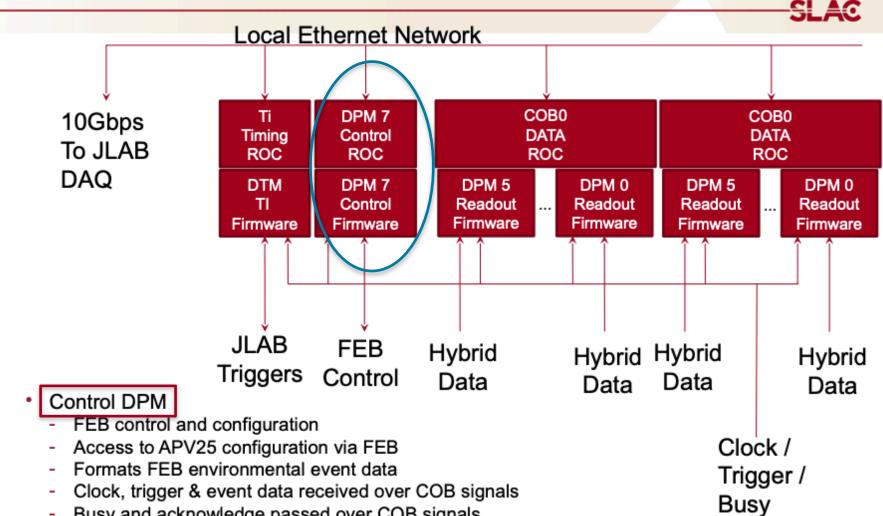

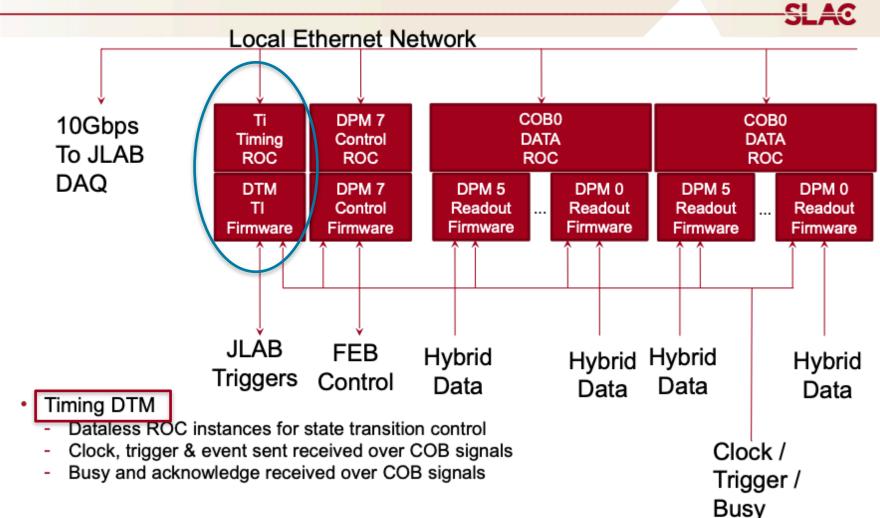

#### **SVT RCE Allocation - 2019 schematics**

- Two COBs utilised in the SVT readout system

- Total 16 RCEs (Data and Control DPMs, 8 DPM per COB)

- 2 DTM (1 DTM per COB)

- 7 RCEs on each COB process data from half SVT

- 8th RCE on COB 0 manages all 10 FEBs Board

- Configuration / Slow controls / Status monitoring

- Clock and trigger distribution to FE boards / Hybrids

- 8th RCE on COB 1 is not used

#### **DAQ Infrastructure architecture**

Schematics of the SVT DAQ Architecture

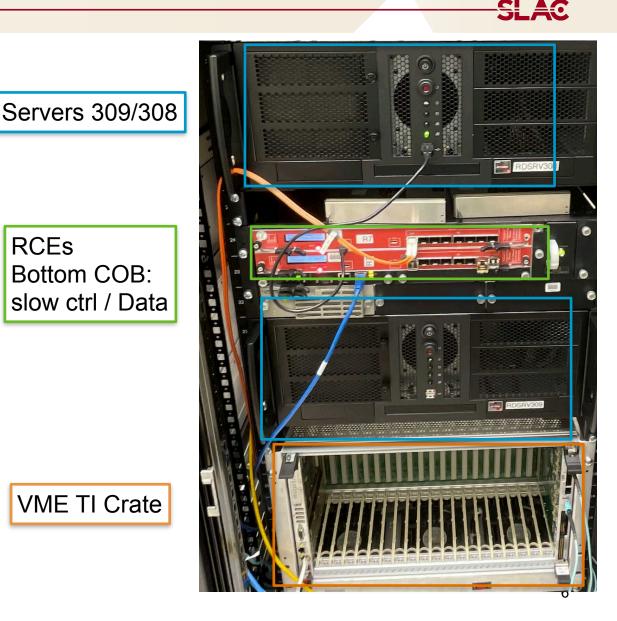

#### Hardware components - ATCA crate - Front

- 2 server machines rdsrv309/308 connected

- Internal dag network between server machines, VME TI Crate and RCEs working and fully functional

- Network sharing in the backplane to be cut

- The 2TiPCle cards have been installed

- Fiber connection from **TI** crate

- Ribbon cable connection to RCEs

- Slow controls to the test stand in SLAC

**RCEs** Bottom COB: slow ctrl / Data

VME TI Crate

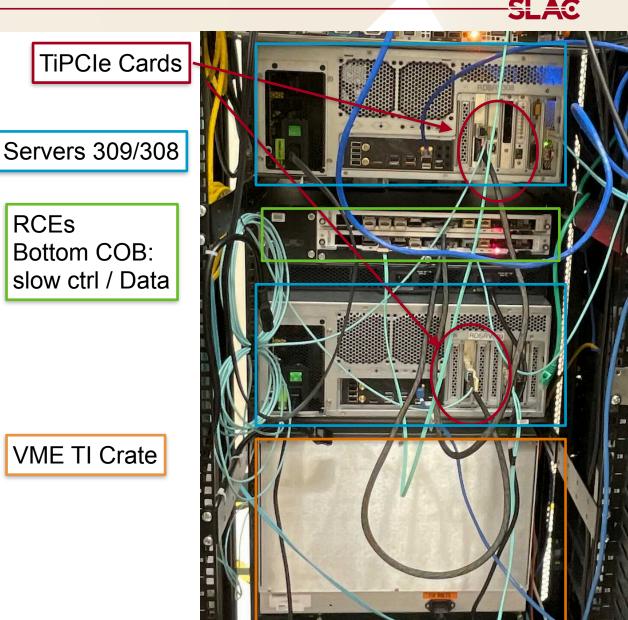

#### Hardware components - ATCA crate - Back

RCEs

- 2 server machines rdsrv309/308 connected

- Internal dag network between server machines. VME TI Crate and RCEs working and fully functional

- Network sharing in the backplane to be cut

- The 2TiPCle cards have been installed

- Fiber connection from TI crate

- Ribbon cable connection to RCEs

- Slow controls to the test stand in SLAC

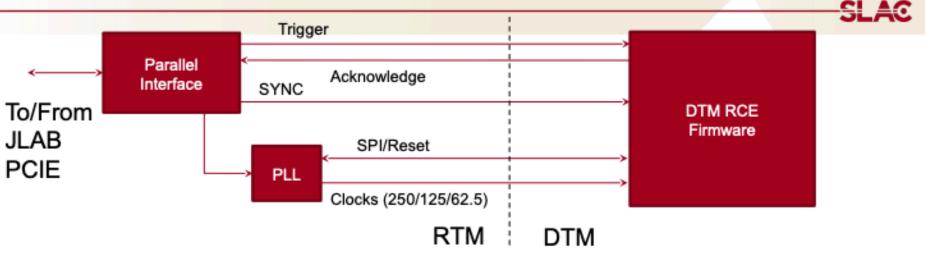

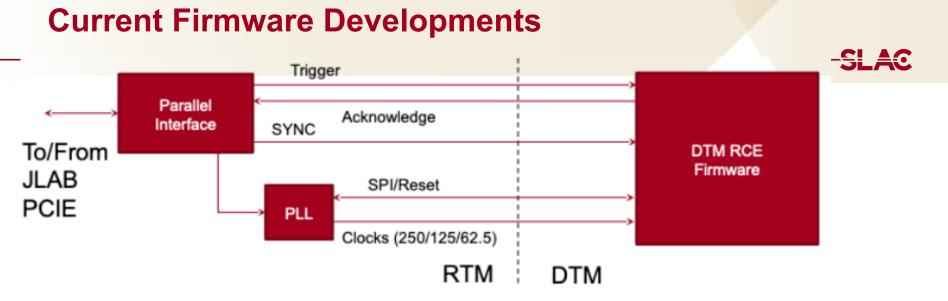

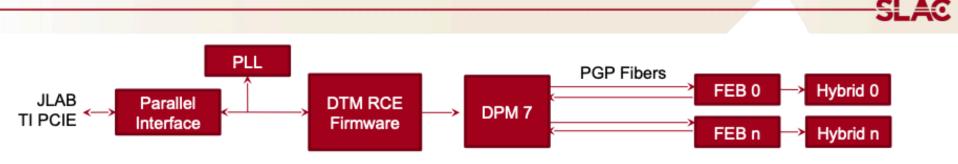

# **SVT Trigger Interface**

- Parallel interface and PLL exist on new RTM

- Fully allocated available signals between RTM and DTM

- 1 high speed pair for trigger & SYNC

- 1 low speed pair for SYNC

- 2 low speed pairs for PLL SPI and Reset signals

- 3 low speed pairs for PLL generated clocks (250/125/62.5 Mhz)

- Observed in the past that sync signal being sent to the DTMs from TIPCIe was out of phase

- This leads to an out of phase sync signal being distributed to the other RCE components

- The full test stand setup at SLAC will be used to develop a FW to cancel out the phase difference in the sync signals

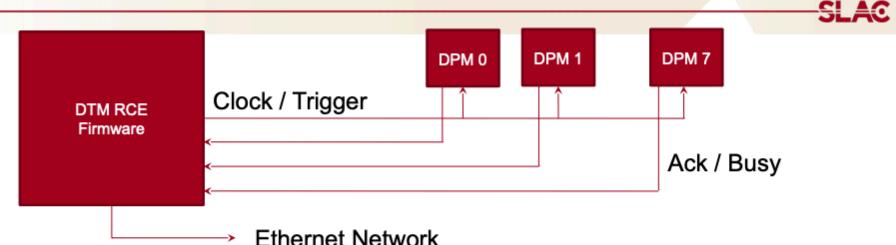

# **SVT Trigger Distribution**

- DTM FPGA has ability to distribute clock and trigger to DPMs

- Clock and trigger wired as fan out to DPMs

- Individual feedback signals from each DPM

- 1 pair for clock fan out

- 1 pair for trigger fan out

- 125Mhz serial protocol transfers 8-bit codes (easily expanded to longer words)

- Used to distribute event codes to DPMs

- System clock sync, APV25 sync & JLAB triggers

- 1 pair for trigger data distribution

- Event and block data

- 1 pair per DPM for feedback

- Readout and trigger acknowledge

- Busy

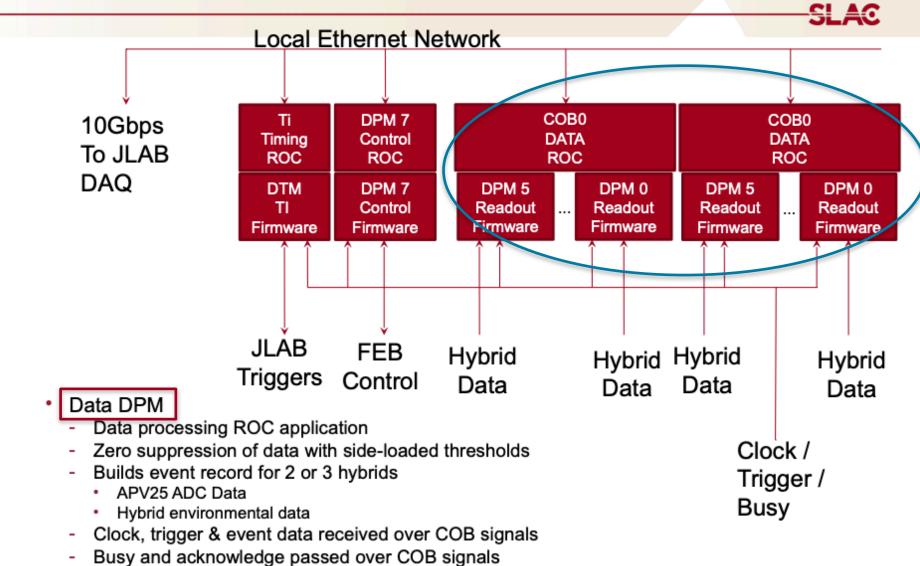

### **ROC Instances On SVT**

#### **ROC Instances On SVT**

#### **ROC Instances On SVT**

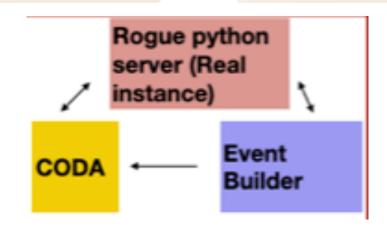

## **Back End - Software applications**

- Rogue:

- General DAQ interface for Configuration / Register monitoring of the whole COB+FEB system

- Local data taking for quick diagnostics

- Inter-process communications: CODA, Epics..

- Updated to newest release from TID-AIR-ES (SLAC)

- <u>v5.8.0</u> (stable)

- Minor changes for HPS Run 2021 interface

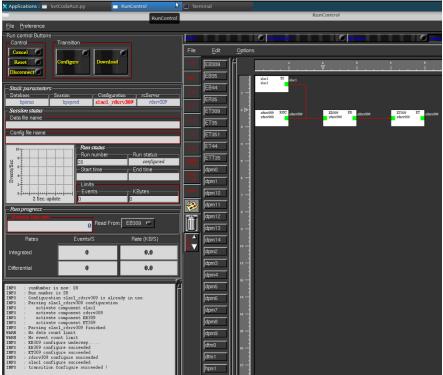

#### **Back End Setup - Integration status**

All current hps daq sw collected here:

#### heavy-photon-daq GIT

- Repository updated and compatible with newest version of Rogue v5.8.0

- Event-Builder compiled successfully against Rogue-Lite (i.e. rogue without python bindings) v5.8.0 (only minor modifications needed so far)

- Sergey successfully compiled and installed CODA in the server machines here at SLAC

#### **Back End Setup - Integration status - CODA**

Integration in CODA almost completed

- Basic configurations have been deployed for baseline data taking

- Currently working to complete the transition to GO state (Prestart Working OK)

- Currently:

- No SaveState in GO / EndOfRun

- No loading of thresholds in Prestart Phase (DAQ Map need to be fixed for SLAC test-stand)

- Check of the

- Configuration is disabled due to issues in read-back of the FEB registers

- Some modifications to the rogue python part needed 16

#### **Back End Setup - Integration status - EPICS**

- Integration with EPICS

- Only Basic checks performed

- Verified communication between Rogue and EPICS:

- I could obtain via "caget" variables pushed by Rogue with EPICS

- Will prepare a full configuration for a IOC Machine to test that all is functioning as expected before the run

SL AC

### **Current Issues - TO DO**

- Some checks need to be performed on the clock from the TIPCle card:

- We are able to read the external clock frequency on the DTMs

- We are able to configure and (partially) talk to the FEBs after configuring with external clock - we see the upTime OK

-> pgp connection seems established

- We receive corrupted data when performing read-back at pre-start stage:

- Need to discuss with Ben/Ryan the source of the issue

|   |     | BusyRateMax                 | RO | UInt32  | 329        | per second |

|---|-----|-----------------------------|----|---------|------------|------------|

| 3 |     | псікоггедкам                | RO | UIIIL32 | 0x7736037  |            |

|   |     | TiClk0Freq                  | RO | Linked  | 125.002    | MHz        |

|   |     | TiClk1FreqRaw               | RO | UInt32  | 0x7736037  |            |

|   |     | TiClk1Freq                  | RO | Linked  | 125.002    | MHz        |

| * | Pci | TiDtm[1]                    |    |         |            |            |

|   |     | enable                      | RW | bool    | True *     |            |

|   | ŀ   | RceVersion                  |    |         |            |            |

|   | ÷   | DtmTiming<br>JLabTimingPcie |    |         |            |            |

|   |     | enable                      | RW | bool    | True *     |            |

|   |     | Mode                        | RW | UInt1   | LocalClk * |            |

|   |     | CodaState                   | RW | UInt3   | DOWNLOAD * |            |

|   |     | SyncAlignDelay              | RW | UInt2   | 0          |            |

|   |     | TiSyncCount                 | RO | UInt32  | 0          |            |

|   |     | TiDownloadSyncCount         | RO | UInt32  | 0          |            |

|   |     | TiPrestartSyncCount         | RO | UInt32  | 0          |            |

|   |     | TiTriggerCount              | RO | UInt32  | 0          |            |

|   |     | BusyTimeRaw                 | RO | UInt32  | 0x0        |            |

|   |     | BusyTime                    | RO | Linked  | 0.000      | %          |

|   |     | BusyTimeMax                 | RO | Linked  | 0.000      | %          |

|   |     | BusyRate                    | RO | UInt32  | 0          | per second |

|   |     | BusyRateMax                 | RO | UInt32  | 0          | per second |

|   |     | TiClk0FreqRaw               | RO | UInt32  | 0x7736318  |            |

|   |     | TiClk0Freq                  | RO | Linked  | 125.003    | MHz        |

|   |     | TiClk1FreqRaw               | RO | UInt32  | 0x7736318  |            |

|   |     | TiClk1Freq                  | RO | Linked  | 125.003    | MHz        |

#### **Status Summary**

- We are completing an SVT DAQ mock-up setup here at SLAC

- Several people contributed, supported and helped so far.

- Currently we are fixing some hiccups..

- Some rogue hardcodes made for the jLab machines

- Daq Mapping should be configured properly for the small system we are testing here

- .. and some more complex issues:

- Issues in reading back FEb configuration when using an external clock

- Full transition to the GO state to be tested

- As soon as CODA is up and running (so the FW developers can work on the sync issue), I'm planning to switch to check EPICs integration

# **Front End Timing Distribution**

- Control DPM forwards timing information to front end boards over PGP

- Clock encoded into serial data stream which the front end board recovers

- Fixed latency path for encoded PLL reset and trigger signals